Fractional t1/e1 support – Maxim Integrated DS21Q55 User Manual

Page 198

Product Preview

DS21Q55

198 of 248

012103

Please contact

or search

http://www.maxim-ic.com

for updated

information.

30. FRACTIONAL T1/E1 SUPPORT

The DS21Q55 can be programmed to output gapped clocks for selected channels in the receive and

transmit paths to simplify connections into a USART or LAPD controller in fractional T1/E1 or ISDN-

PRI applications. This is accomplished by assigning an alternate function to the RCHCLK and TCHCLK

pins. When the gapped clock feature is enabled, a gated clock is output on the RCHCLK and/or TCHCLK

pins. The channel selection is controlled via the special per-channel control registers. No clock is

generated at the F-bit position. The receive and transmit paths have independent enables. Channel formats

supported include 56kbps and 64kbps.

When 56kbps mode is selected, the clock corresponding to the data/control bit in the channel is omitted.

Only the seven most significant bits of the channel have clocks.

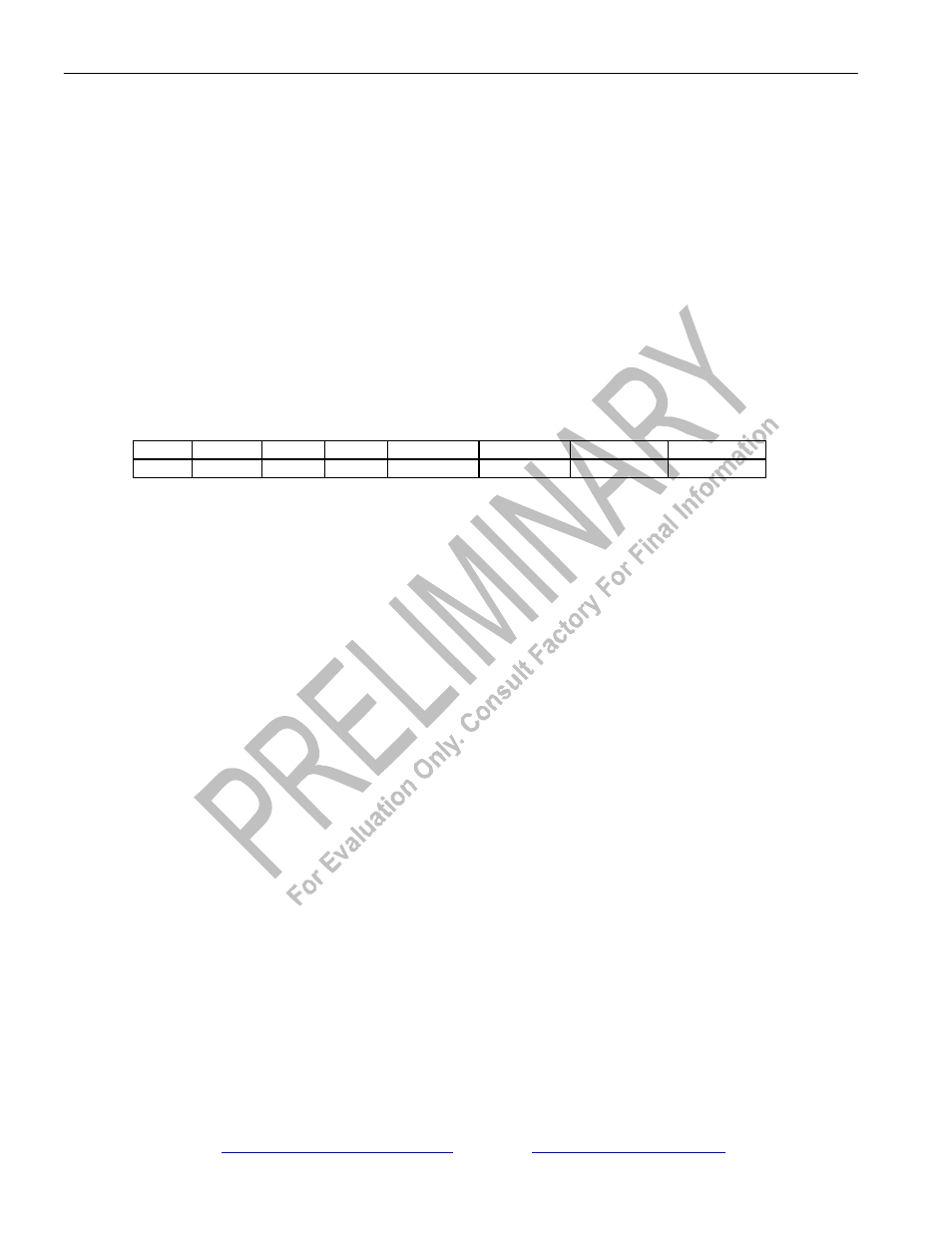

Register Name:

CCR3

Register Description:

Common Control Register 3

Register Address:

72h

Bit #

7

6

5

4

3

2

1

0

Name

-

-

-

-

TDATFMT

TGPCKEN

RDATFMT

RGPCKEN

Default

0

0

0

0

0

0

0

0

Bit 0/Receive Gapped-Clock Enable (RGPCKEN).

0 = RCHCLK functions normally

1 = enable gapped-bit clock output on RCHCLK

Bit 1/Receive Channel-Data Format (RDATFMT).

0 = 64kbps (data contained in all 8 bits)

1 = 56kbps (data contained in 7 out of the 8 bits)

Bit 2/Transmit Gapped-Clock Enable (TGPCKEN).

0 = TCHCLK functions normally

1 = enable gapped-bit clock output on TCHCLK

Bit 3/Transmit Channel-Data Format (TDATFMT).

0 = 64kbps (data contained in all 8 bits)

1 = 56kbps (data contained in 7 out of the 8 bits)

Bit 4/Unused, must be set to zero for proper operation.

Bit 5/Unused, must be set to zero for proper operation.

Bit 6/Unused, must be set to zero for proper operation.

Bit 7/Unused, must be set to zero for proper operation.