Programmable backplane clock synthesizer – Maxim Integrated DS21Q55 User Manual

Page 197

Product Preview

DS21Q55

197 of 248

012103

Please contact

or search

http://www.maxim-ic.com

for updated

information.

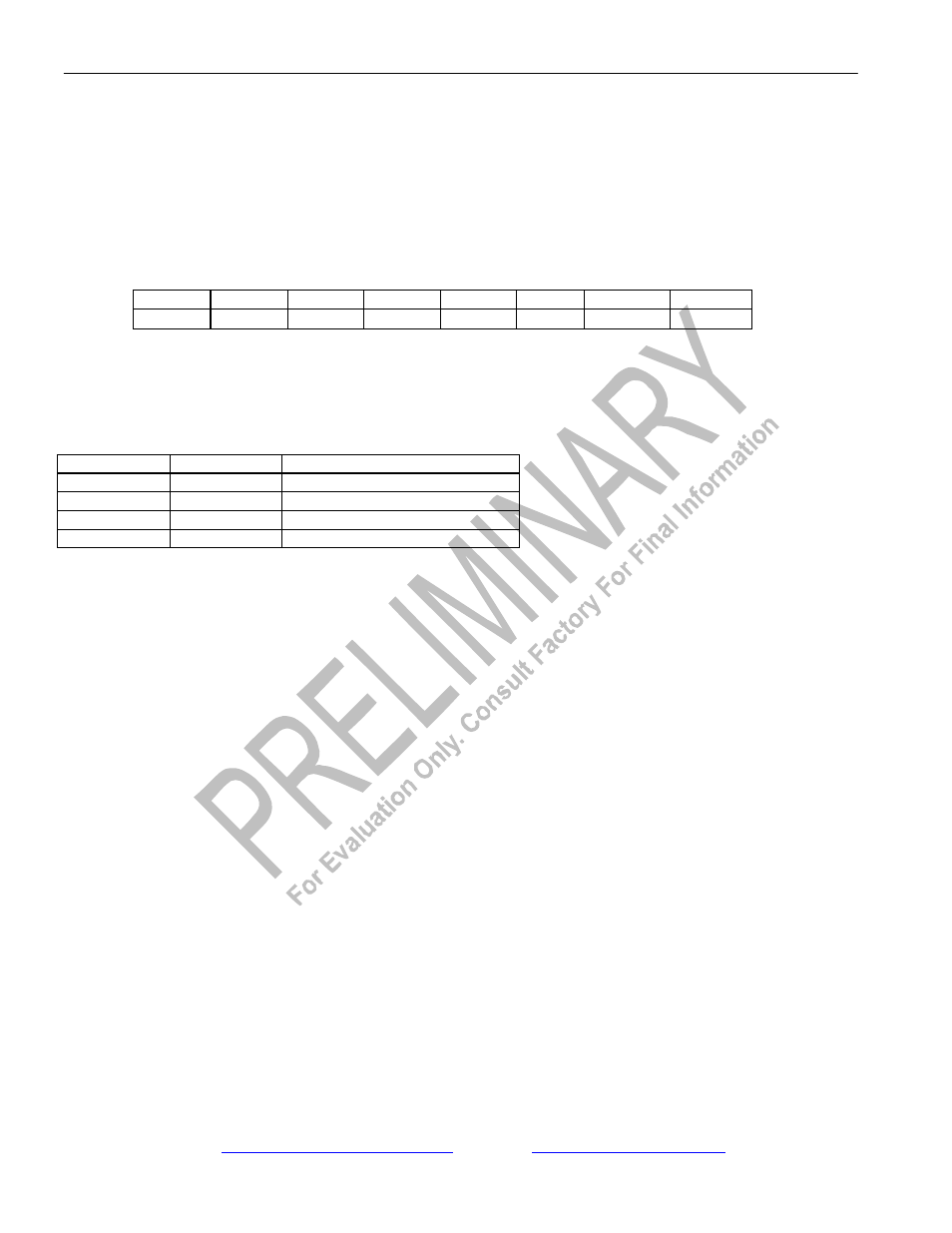

29. PROGRAMMABLE BACKPLANE CLOCK SYNTHESIZER

The DS21Q55 contains an on-chip clock synthesizer that generates a user-selectable clock referenced to

the recovered receive clock (RCLK). The synthesizer uses a phase- locked loop to generate low-jitter

clocks. Common applications include generation of port and back plane system clocks.

Register Name:

CCR2

Register Description:

Common Control Register 2

Register Address:

71h

Bit #

7

6

5

4

3

2

1

0

Name

-

-

-

-

-

BPCS1

BPCS0

BPEN

Default

0

0

0

0

0

0

0

0

Bit 0/Back Plane Clock Enable (BPEN).

0 = disable BPCLK pin (Pin held at logic 0)

1 = enable BPCLK pin

Bits 1 to 2/Back Plane Clock Selects (BPCS0, BPCS1).

BPCS1

BPCS0

BPCLK FREQUENCY (MHz)

0

0

16.384

0

1

8.192

1

0

4.096

1

1

2.048

Bit 3/Unused, must be set to zero for proper operation.

Bit 4/Unused, must be set to zero for proper operation.

Bit 5/Unused, must be set to zero for proper operation.

Bit 6/Unused, must be set to zero for proper operation.

Bit 7/Unused, must be set to zero for proper operation.