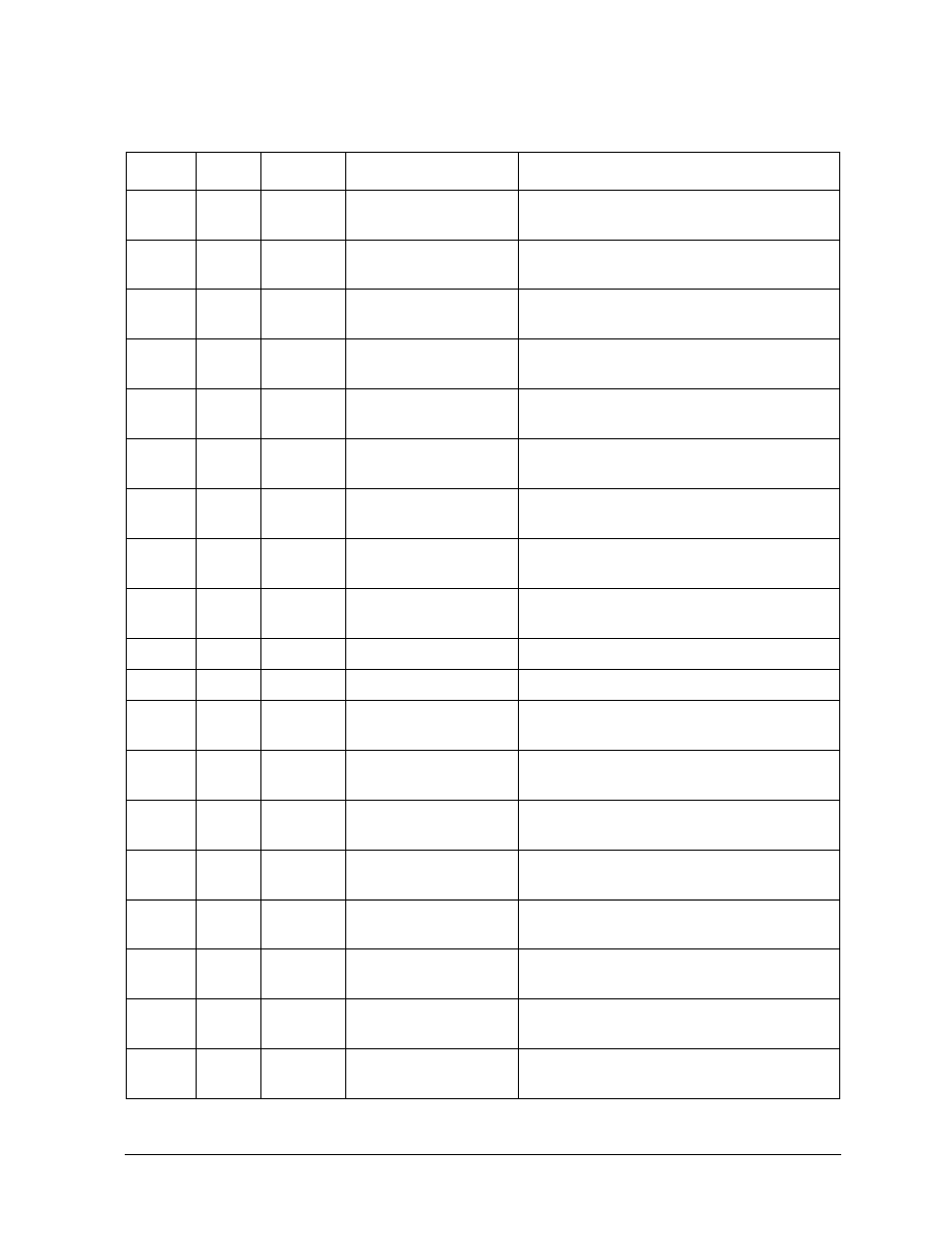

Table row, 1n27, Sys bd – HP B1000 User Manual

Page 63: Cpun itimer test, Cpu n is starting its interval timer self-test, 1n28, Cpun multi-media, 1n29, Cpun shadow reg, Cpu n is starting its shadow register self-test

Chapter 3

63

Troubleshooting

Selftest Failures

TST

1n27

SYS BD

CPU

n itimer test

CPU n is starting its interval timer

self-test.

TST

1n28

SYS BD

CPU

n multi-media

CPU n is starting its multi-media

instructions self-test.

TST

1n29

SYS BD

CPU

n shadow reg

CPU n is starting its shadow register

self-test.

TST

1n2A

SYS BD

CPU

n diagnse reg

CPU n is starting its diagnose register

self-test.

TST

1n2B

SYS BD

CPU

n rdr test

CPU n is starting its remote diagnose

register self-test.

TST

1n2C

SYS BD

CPU

n bypass test

CPU n is starting its integer bypass

operation self-test.

TST

1n30

SYS BD

CPU

n start est

CPU n is starting its early (pre-memory)

self-tests.

WRN

1n31

SYS BD

CPU

n skip est

CPU n is bypassing its early self-tests to

save time.

FLT

1n32

SYS BD

CPU

n bad tst mod

CPU n detected an unsupported system

mode.

INI

1n3C

SYS BD

CPU

n initialize

CPU n is initializing after self-tests.

TST

1n3E

SYS BD

CPU

n exit est

CPU n finished its early self-tests.

TST

1nA0

SYS BD

CPU

n fpu tests

CPU n is starting its floating-point unit

self-tests.

TST

1nA1

SYS BD

CPU

n fpu reg tst

CPU n is starting its floating-point

register self-test.

TST

1nA2

SYS BD

CPU

n fpu inst

CPU n is starting its floating-point

instruction self-test.

TST

1nA3

SYS BD

CPU

n fpu traps

CPU n is starting its floating-point trap

self-test.

TST

1nA4

SYS BD

CPU

n fpu misc

CPU n is starting its floating-point

miscellaneous operations self-test.

TST

1nA5

SYS BD

CPU

n fpu bypass

CPU n is starting its floating-point

bypassing self-test.

TST

1nB1

SYS BD

CPU

n TLB RAM tst

CPU n is starting its TLB register

self-test.

TST

1nB2

SYS BD

CPU

n TLB trans

CPU n is starting its TLB translation

self-test.

Table 3-2. Chassis Codes for B1000/C3000 Workstations

Ostat

Code

FRU

Message

Description