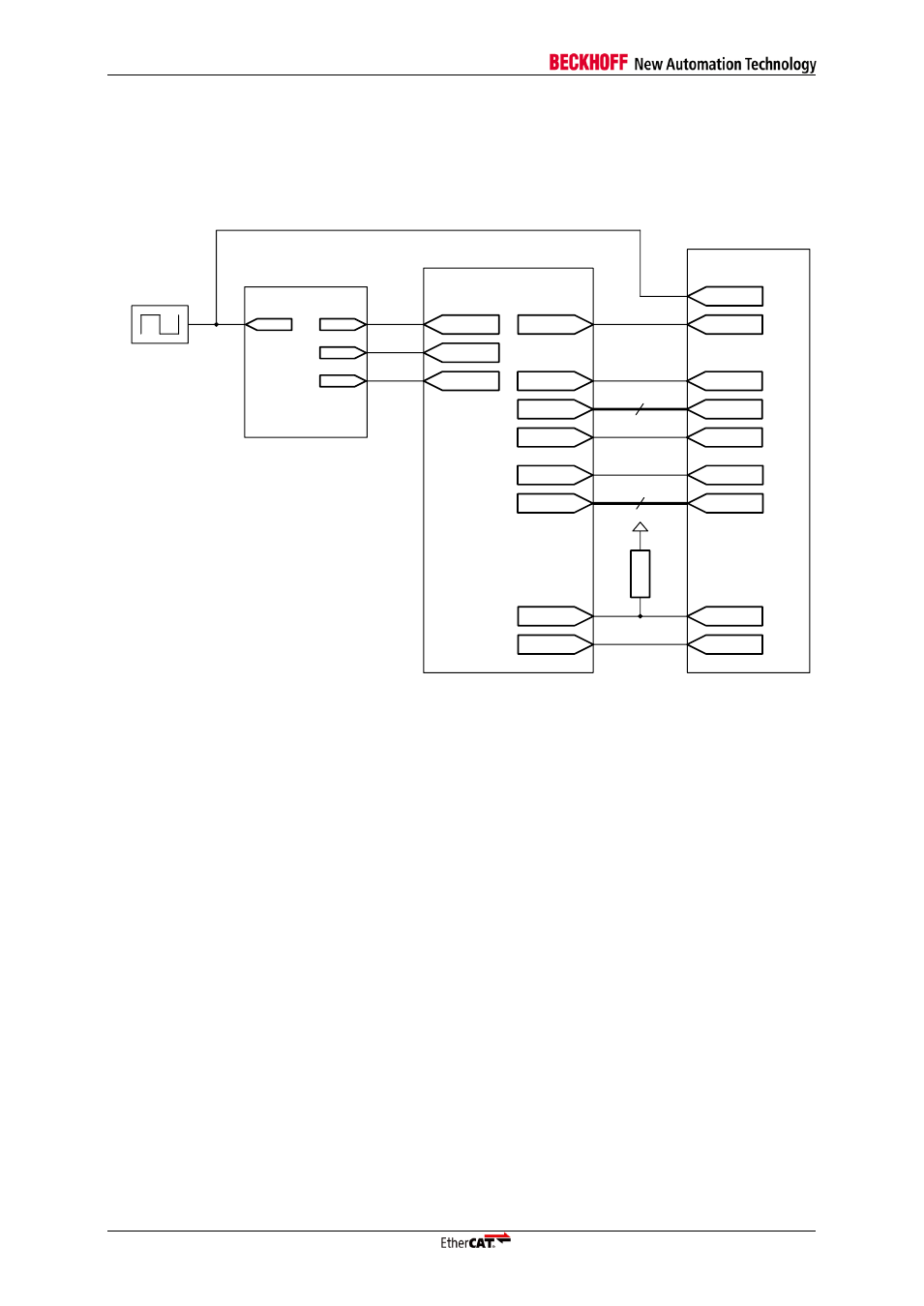

2 rmii example schematic, Rmii example schematic, Figure 33: rmii example schematic – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 86: Ethercat ip core ethernet phy, Dcm/pll, 50 mhz

Ethernet Interface

III-74

Slave Controller

– IP Core for Xilinx FPGAs

9.3.2

RMII example schematic

Refer to chapter 8.4 for more information on special markings (!). Take care of proper PHY address

configuration.

EtherCAT IP Core

Ethernet PHY

RMII_RX_DV

RMII_RX_DATA[1:0]

RMII_RX_ERR

RMII_TX_ENA

RMII_TX_DATA[1:0]

CRS_DV

RXD[1:0]

RX_ER

TX_EN

TXD[1:0]

REF_CLK

nRMII_LINK

LINK_STATUS

!

CLK25

DCM/PLL

CLK_IN

CLK25

CLK100

CLK100

50 MHz

CLK50

CLK50

MDIO

MCLK

MDIO

MDC

4

K

7

V

CC I/O

Figure 33: RMII example schematic

This manual is related to the following products: