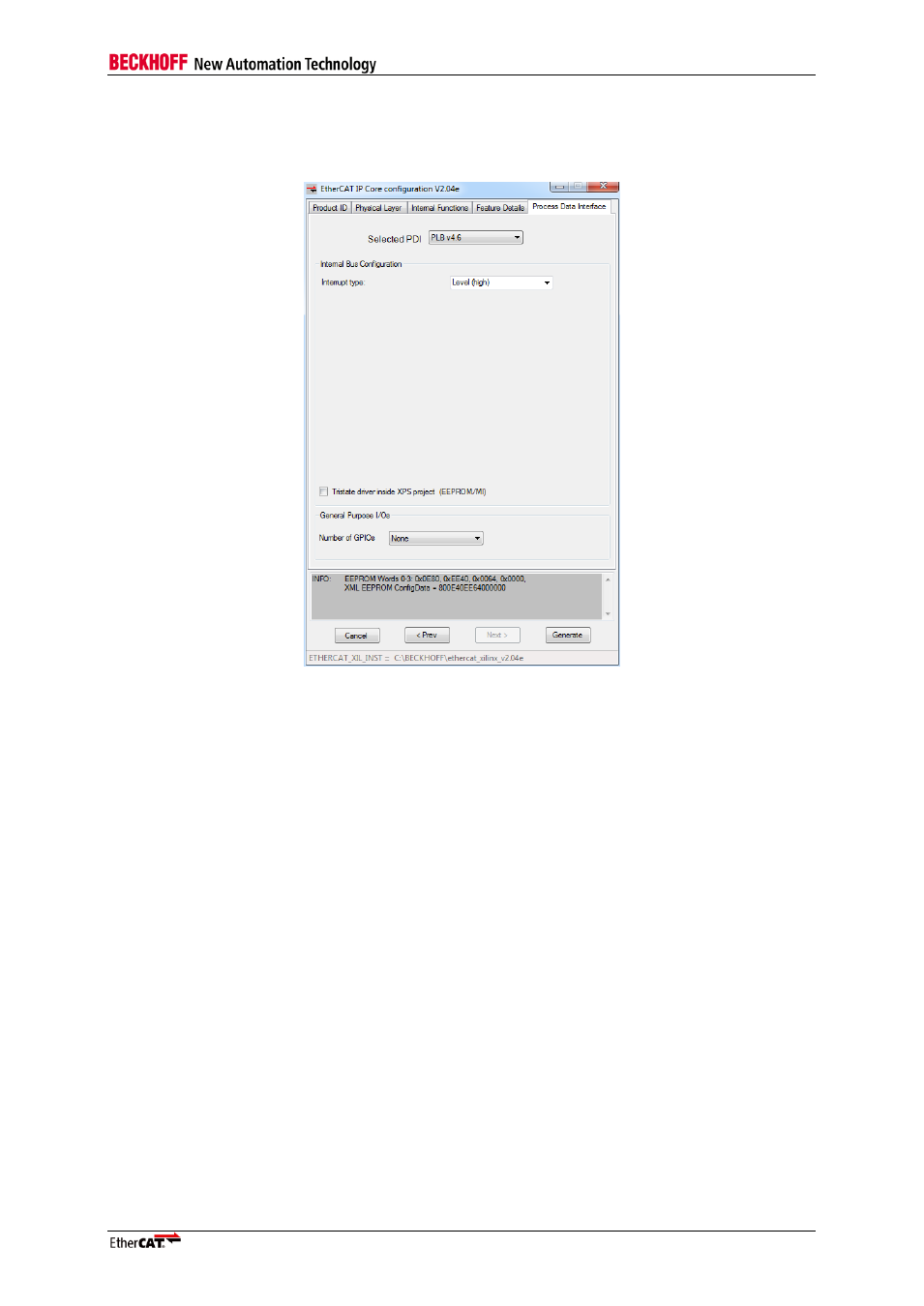

5 processor local bus (plb) configuration, Figure 22: register pdi, Plb interface configuration – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 55

IP Core Configuration

Slave Controller

– IP Core for Xilinx FPGAs

III-43

5.1.5.5

Processor Local Bus (PLB) Configuration

The PLB v4.6 PDI connects the IP Core with a PLB Master (e.g. Xilinx MicroBlaze

TM

). The data bus

with is 32 bit, and the address bus is also 32 bit wide.

Figure 22: Register PDI

– PLB Interface Configuration

Interrupt type

Select the usage type of the interrupt signal (level or edge). Since the main interrupt can have different

sources, a level based interrupt is typically required.

Tristate driver inside XPS project (EEPROM/MII)

This option is available if the Tristate drivers are not integrated in the core (Physical Layer tab). It

allows to export the IN/OUT/ENA tristate signals to higher levels above the XPS, or implement the

tristate driver in the XPS.

This additional option is offered in

the “Configure IP” dialog of the EtherCAT IP Core instance inside

EDK.