BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 24

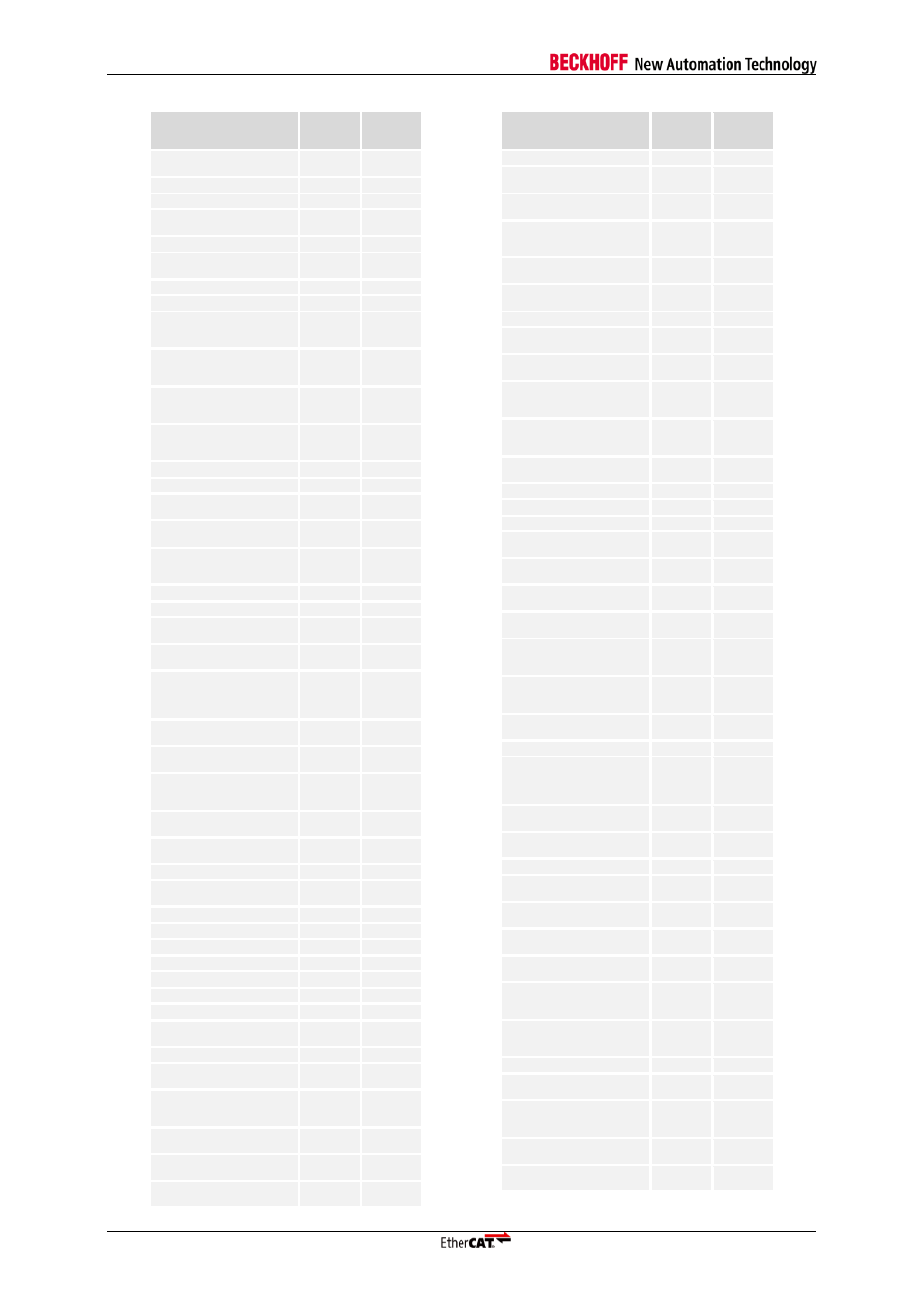

Features and Registers

III-12

Slave Controller

– IP Core for Xilinx FPGAs

Feature

IP Core

Xilinx

®

V2.04e

IP Core

Xilinx

V2.04d

Output high-Z if WD

expired

User logic

User logic

Output 0 if WD expired

x

x

Output with EOF

x

x

Output with DC

SyncSignals

x

x

Input with SOF

x

x

Input with DC

SyncSignals

x

x

SPI Slave PDI

x

x

Max. SPI clock [MHz]

30

30

SPI modes

configurable

(0x0150[1:0])

x

x

SPI_IRQ driver

configurable

(0x0150[3:2])

x

x

SPI_SEL polarity

configurable

(0x0150.4)

x

x

Data out sample mode

configurable

(0x0150.5)

x

x

Busy signaling

-

-

Wait State byte(s)

x

x

Number of address

extension byte(s)

any

any

2/4 Byte SPI master

support

x

x

Extended error

detection (read busy

violation)

x

x

SPI_IRQ delay

x

x

Status indication

x

x

EEPROM_

Loaded signal

-

-

Asynchronous µController

PDI

8/16 bit

8/16 bit

Extended µC

configuration bits

0x0150[7:4],

0x0152:0x0153

x

x

ADR[15:13] available

(000

b

if not available)

x

x

EEPROM_Loaded

signal

-

-

RD polarity

configurable

(0x0150.7)

-

-

Read BUSY delay

(0x0152.0)

x

x

Write after first edge

(0x0152.2)

x

x

Synchronous µController PDI

-

-

EEPROM_

Loaded signal

On-Chip Bus PDI

x

x

Avalon

®

-

-

OPB

®

x

x

PLB v4.6

®

x

x

AXI3

TM

-

-

AXI4

TM

-

-

AXI4 LITE

TM

-

-

Bus clock [MHz]

(N=1,2,3,…)

N*25

N*25

Data bus width [bits]

32

32

Prefetch cycles

1/2/4

(OPB)

1/2/4

(OPB)

DC SyncSignals

available directly and

as IRQ

x

x

Bus clock multiplier in

register 0x0150[6:0]

x

x

EEPROM_

Loaded signal

-

-

EtherCAT Bridge (port 3,

EBUS/MII)

-

-

Feature

IP Core

Xilinx

®

V2.04e

IP Core

Xilinx

V2.04d

General Purpose I/O

x

x

GPO bits

0/8/16/

32/64

0/8/16/

32/64

GPI bits

0/8/16/

32/64

0/8/16/

32/64

GPIO available

independent of PDI or

port configuration

x

x

GPIO available without

PDI

x

x

Concurrent access to

GPO by ECAT and PDI

x

x

ESC Information

Basic Information

(0x0000:0x0006)

x

x

Port Descriptor

(0x0007)

x

x

ESC Features

supported

(0x0008:0x0009)

x

x

Extended ESC Feature

Availability in User

RAM (0x0F80 ff.)

x

x

Write Protection

(0x0020:0x0031)

c

c

Data Link Layer Features

ECAT Reset (0x0040)

c

c

PDI Reset (0x0041)

c

c

ESC DL Control

(0x0100:0x0103) bytes

4

4

EtherCAT only mode

(0x0100.0)

x

x

Temporary loop control

(0x0100.1)

x

x

FIFO Size configurable

(0x0100[18:16])

x

x

Configured Station

Address

(0x0010:0x0011)

x

x

Configured Station

Alias (0x0100.24,

0x0012:0x0013)

x

x

Physical Read/Write

Offset (0x0108:0x0109)

c

c

Application Layer Features

Extended AL

Control/Status bits

(0x0120[15:5],

0x0130[15:5])

x

x

AL Status Emulation

(0x0140.8)

x

x

AL Status Code

(0x0134:0x0135)

c

c

Interrupts

ECAT Event Mask

(0x0200:0x0201)

x

x

AL Event Mask

(0x0204:0x0207)

c

c

ECAT Event Request

(0x0210:0x0211)

x

x

AL Event Request

(0x0220:0x0223)

x

x

SyncManager

activation changed

(0x0220.4)

x

x

SyncManager

watchdog expiration

(0x0220.6)

x

x

Error Counters

RX Error Counter

(0x0300:0x0307)

x

x

Forwarded RX Error

Counter

(0x0308:0x030B)

x

x

ECAT Processing Unit

Error Counter (0x030C)

c

c

PDI Error Counter

(0x030D)

c

c