BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 70

IP Core Signals

III-58

Slave Controller

– IP Core for Xilinx FPGAs

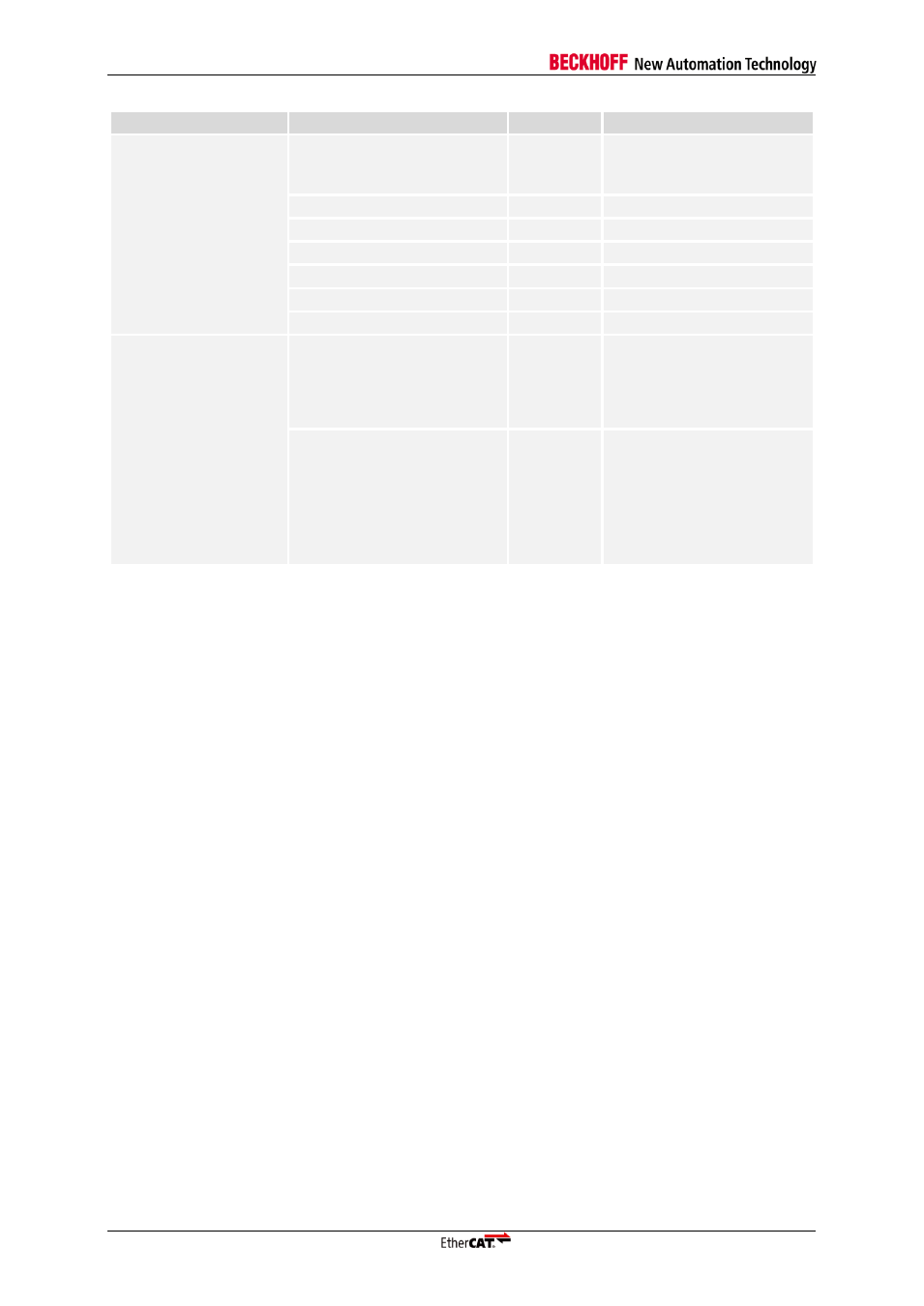

Condition

Name

Direction

Description

Port2 = MII

nMII_LINK2

INPUT

0: 100 Mbit/s (Full

Duplex) link at port 2

1: no link at port 2

MII_RX_CLK2

INPUT

Receive clock port 2

MII_RX_DV2

INPUT

Receive data valid port 2

MII_RX_DATA2[3:0]

INPUT

Receive data port 2

MII_RX_ERR2

INPUT

Receive error port 2

MII_TX_ENA2

OUTPUT

Transmit enable port 2

MII_TX_DATA2[3:0]

OUTPUT

Transmit data port 2

Port2 = MII and TX

Shift activated

MII_TX_CLK2

INPUT

Transmit clock port 2 for

automatic TX Shift

configuration. Set to 0 for

manual TX Shift

configuration.

MII_TX_SHIFT2[1:0]

INPUT

Manual TX shift

configuration port 2.

Additional TX signal delay:

00: 0 ns

01: 10 ns

10: 20 ns

11: 30 ns

This manual is related to the following products: