BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 76

IP Core Signals

III-64

Slave Controller

– IP Core for Xilinx FPGAs

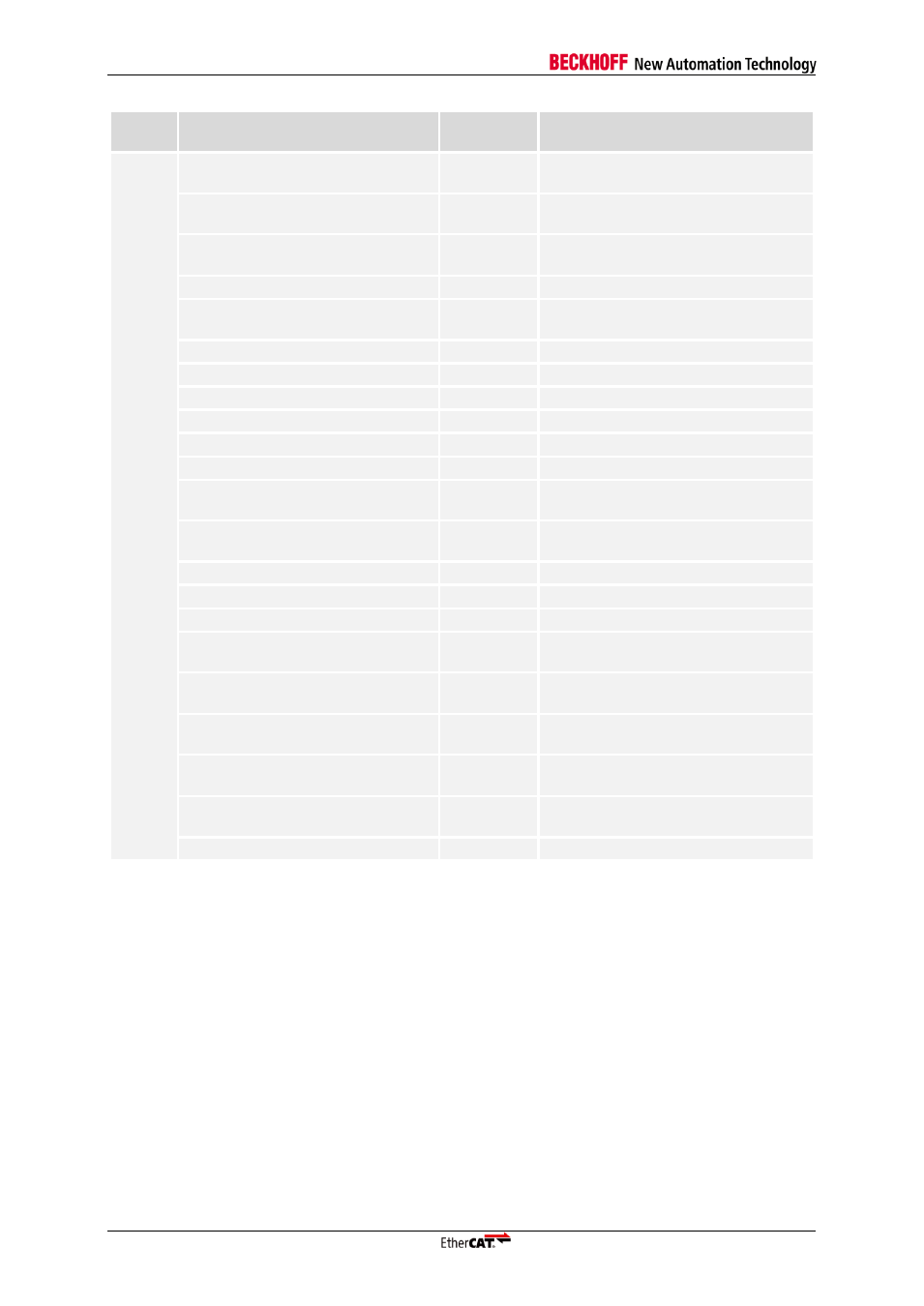

Condi-

tion

Name

Direction

Description

PDI_PLB_rdPendReq

INPUT

PLB pending read bus request

(ignored)

PDI_PLB_wrPendPri(0:1)

INPUT

PLB pending write request priority

(ignored)

PDI_PLB_rdPendPri(0:1)

INPUT

PLB pending read request priority

(ignored)

PDI_PLB_reqPri(0:1)

INPUT

PLB current request priority (ignored)

PDI_PLB_TAttribute(0:15)

INPUT

PLB transfer attribute bus (must be

0x0000)

PDI_PLB_Sl_addrAck

OUTPUT

Slave address acknowledge

PDI_PLB_Sl_SSize(0:1)

OUTPUT

Slave data bus size (always 00)

PDI_PLB_Sl_wait

OUTPUT

Slave wait

PDI_PLB_Sl_rearbitrate

OUTPUT

Slave rearbitrate bus (always 0)

PDI_PLB_Sl_wrDAck

OUTPUT

Slave write data acknowledge

PDI_PLB_Sl_wrComp

OUTPUT

Slave write transfer complete

PDI_PLB_Sl_wrBTerm

OUTPUT

Slave terminate write burst transfer

(always 0)

PDI_PLB_Sl_rdDBus

(0:C_SPLB_DWIDTH-1)

OUTPUT

Slave read data bus

PDI_PLB_Sl_rdWdAddr(0:3)

OUTPUT

Slave read word address (always 0)

PDI_PLB_Sl_rdDAck

OUTPUT

Slave read data acknowledge

PDI_PLB_Sl_rdComp

OUTPUT

Slave read transfer complete

PDI_PLB_Sl_rdBTerm

OUTPUT

Slave terminate read burst transfer

(always 0)

PDI_PLB_Sl_MBusy

(0:C_SPLB_NUM_MASTERS-1)

OUTPUT

Slave busy

PDI_PLB_Sl_MWrErr

(0:C_SPLB_NUM_MASTERS-1)

OUTPUT

Slave write error (always 0)

PDI_PLB_Sl_MRdErr

(0:C_SPLB_NUM_MASTERS-1)

OUTPUT

Slave read error (always 0)

PDI_PLB_Sl_MIRQ

(0:C_SPLB_NUM_MASTERS-1)

OUTPUT

Slave interrupt (always 0)

PDI_PLB_IRQ_MAIN

OUTPUT

Interrupt

The address range of the EtherCAT IP core should span at least 64 Kbyte (e.g., C_BASEADDR =

0x00010000 and C_HIGHADDR=0x0001FFFF). A larger address range results in less address

decoding logic.