BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 63

FPGA Resource Consumption

Slave Controller

– IP Core for Xilinx FPGAs

III-51

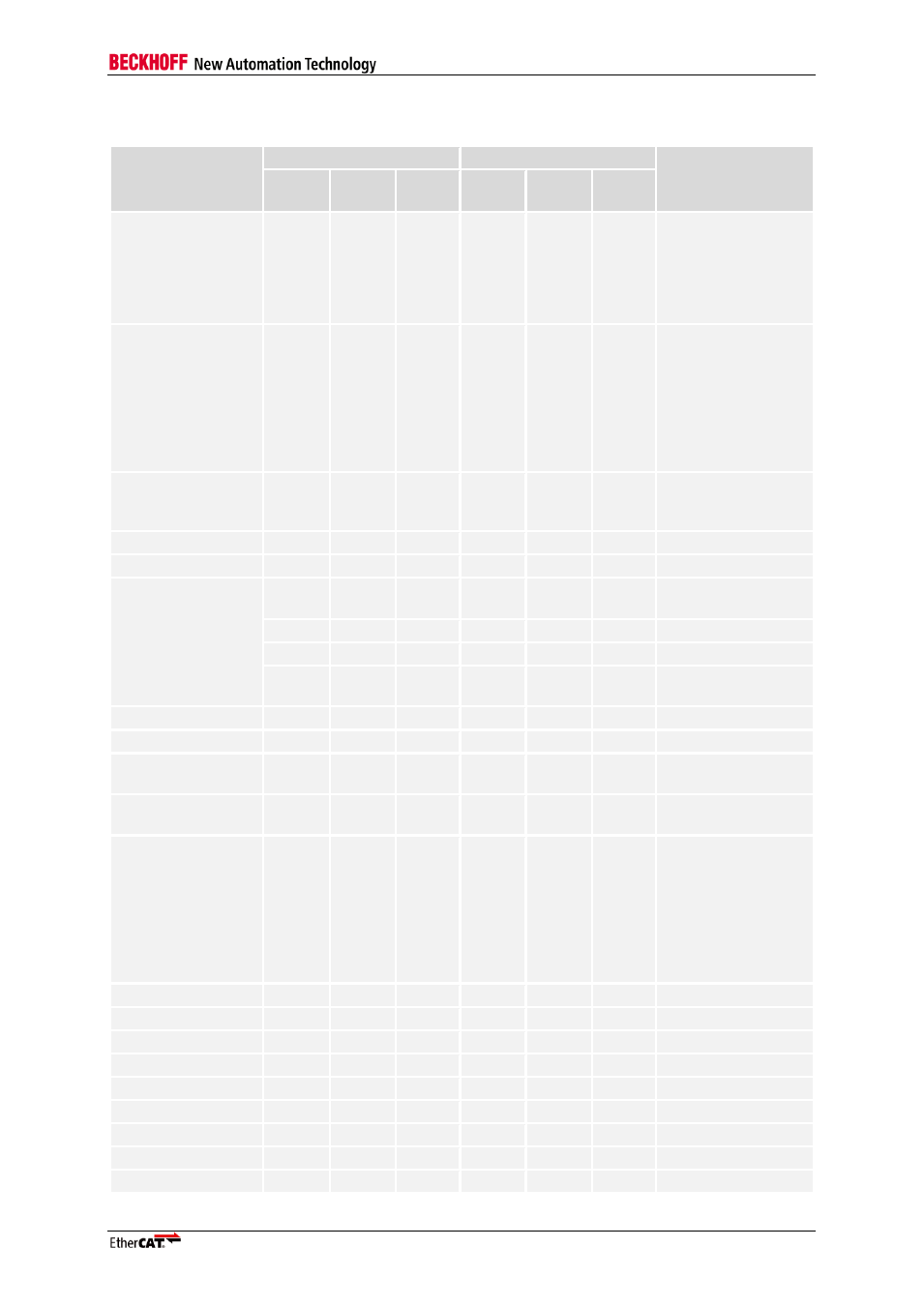

Table 15: Approximate resource requirements for main configurable functions

Configurable

Function

Spartan-3E

Spartan-6

Details

Slices

Reg.

Log.

LUT4

Slices

Reg.

Log.

LUT6

Minimum

Configuration

2,400

1,800

2,800

800

2,000

2,100

0 x SM, 0 x FMMU,

small register

preset, no DC, PDI:

32 Bit digital I/O, 1

kByte DPRAM, 1

port MII

Maximum

Configuration

14,000

14,000

21,000 5,900

13,200 17,300 8 x SM, 8 x FMMU,

large register preset

plus all features

except for EEPROM

Emulation, DC 64

bit, PDI: SPI, GPIO,

60 kByte DPRAM, 3

ports MII

Additional port

700

550

900

250

550

600

all port features

enabled (without DC

Receive times)

SyncManager

350

200

550

150

200

400

per SyncManager

FMMU

400

400

600

200

400

450

per FMMU

Distributed Clocks

200

150

150

150

400

200

Receive time per

port

2,100

2,100

2,800

800

2,200

2,300

32 bit

3,300

3,600

4,300

1,600

3,600

3,900

64 bit

650

350

450

100

350

200

SyncManager Event

Times

Register preset

small

-

-

-

-

-

-

reference

medium

300

250

200

0

250

200

according to small

register preset

large

600

550

650

200

550

550

according to small

register preset

PHY features

900

400

850

150

400

500

All MII features:

Management

Interface, MI link

detection and

configuration, TX

Shift, and enhanced

link detection (3

ports)

DPRAM

300

0

0

50

0

450

60 KB (BlockRAM)

PDI

32 Bit Digital I/O

400

250

250

100

200

200

SPI

250

250

350

100

250

300

8 Bit µController

150

150

200

50

150

150

16 Bit µController

200

200

250

50

150

200

PLB

550

400

450

150

400

250

50 MHz, 32 Bit

OPB

600

300

450

100

300

350

50 MHz, 32 Bit

GPIO

550

350

250

50

350

200

8 Byte