8 connection with 8 bit µcontrollers, Connection with 8 bit µcontrollers – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 107

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-95

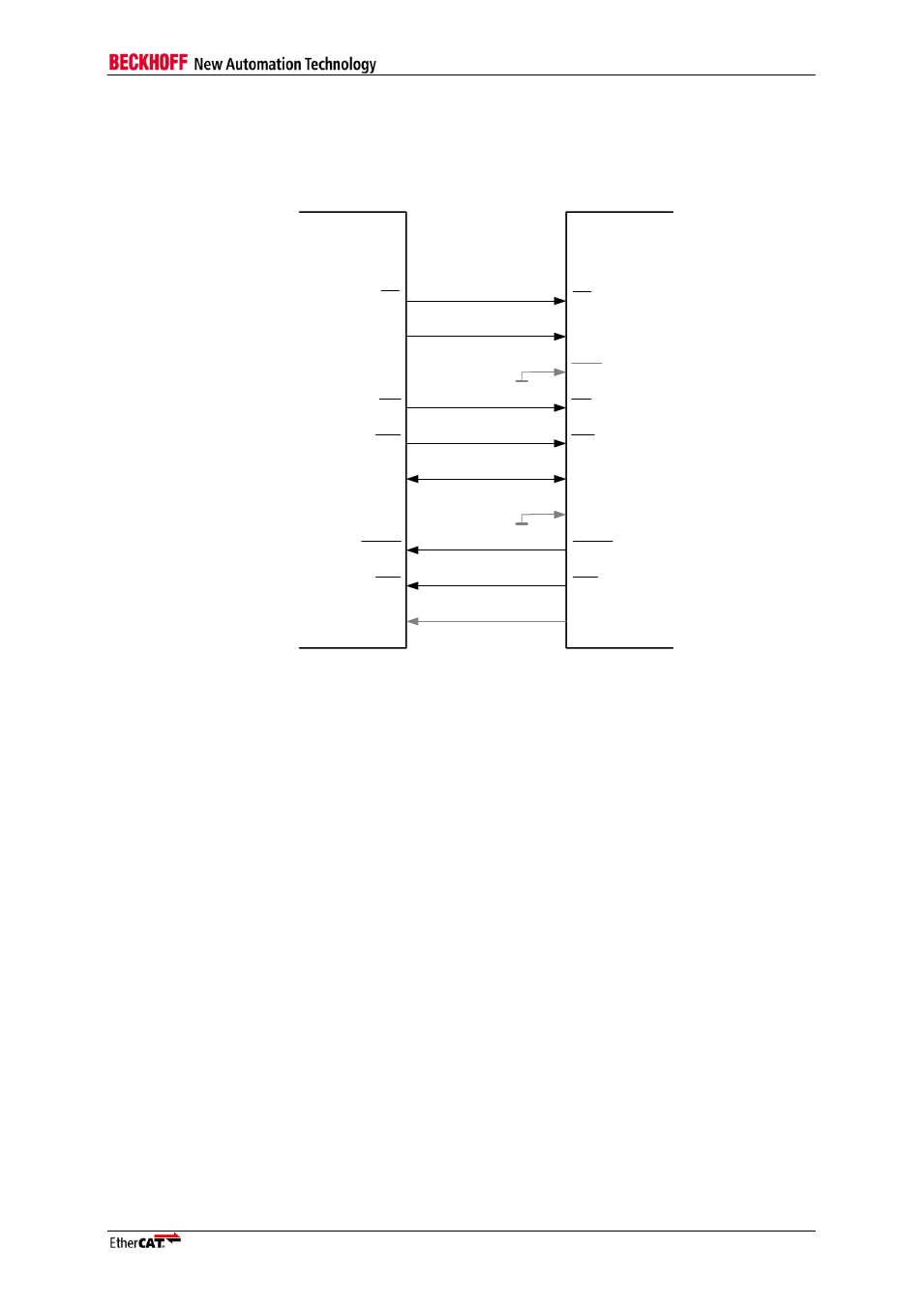

10.3.8 Connection with 8 bit µControllers

If the ESC is connected to 8 bit µControllers, the BHE signal as well as the DATA[15:8] signals are not

used.

CS

CS

ADR[15:0]

RD

BUSY

WR

ADR[15:0]

RD

BUSY

DATA[15:8] (unused)

WR

8 bit µController, async

EtherCAT device

IRQ

IRQ

BHE (unused)

General purpose input

EEPROM_Loaded

optional

DATA[7:0]

DATA[7:0]

Figure 48: Connection with 8 bit µControllers (BHE and DATA[15:8] should not be left open)

This manual is related to the following products: