1 configuration and resource consumption, 2 functionality, 3 implementation – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 60: Configuration and resource consumption, Functionality, Implementation

Example Designs

III-48

Slave Controller

– IP Core for Xilinx FPGAs

6.2

Avnet Xilinx Spartan-6 LX150T Development Kit with PLB/AXI

6.2.1

Configuration and resource consumption

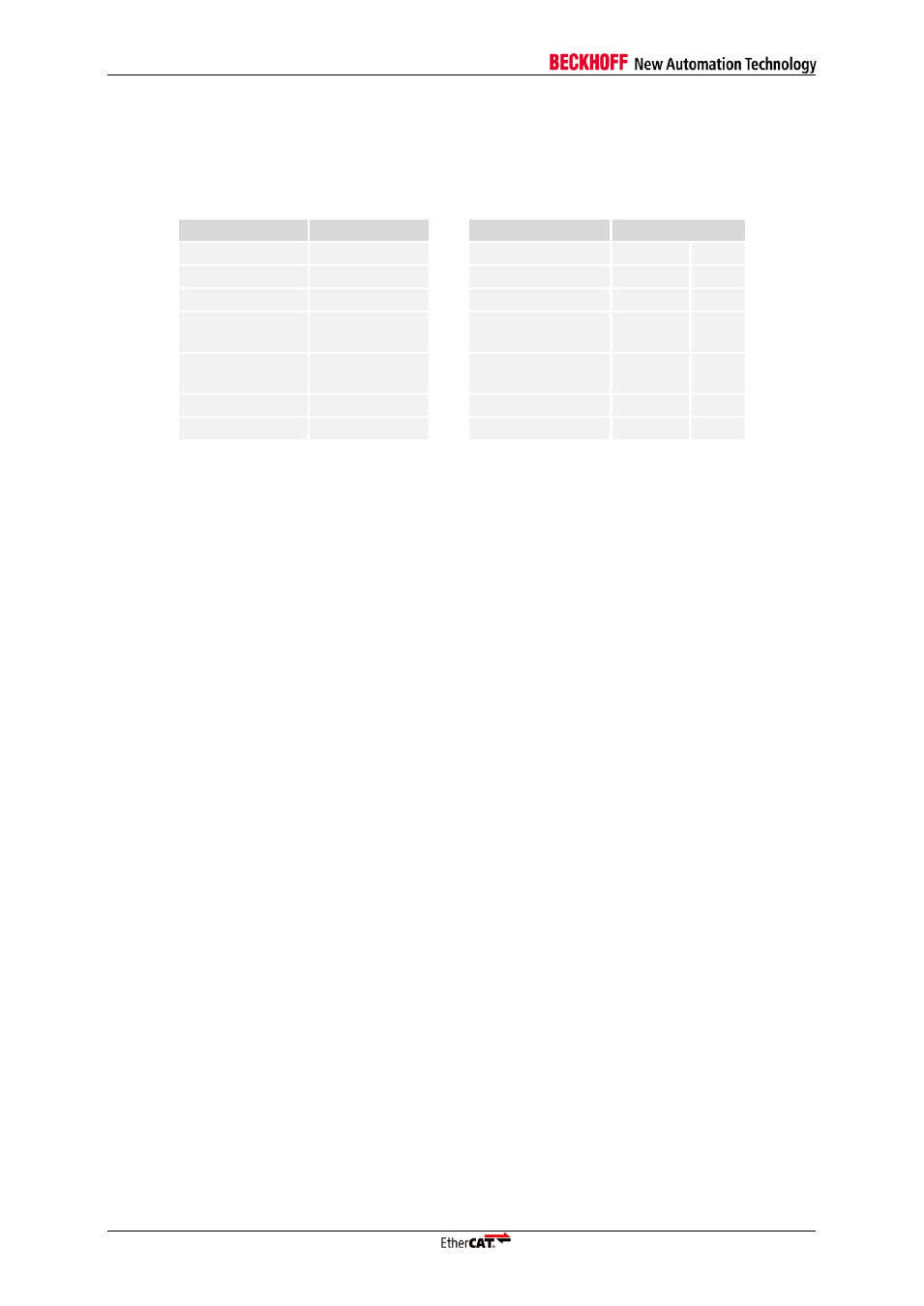

Table 14: Resource consumption Avnet LX150T example design

Configuration

Resources

XC6SLX150T

FMMU

3

Slices

5,100

22 %

SyncManager

4

Slice FF

10,575

5 %

RAM

1 KB

LUT

13,418

14 %

Register set

Large + Run

LED + MI

I/O

73

18 %

Distributed

Clocks

32 bit

Block RAM

17

6 %

PDI

PLB, 50 MHz

BUFGMUX

6

37 %

PLL

1

16 %

6.2.2

Functionality

Attach the FMC ISMNET module to FMC1 connector of LX150T base board. Populate jumper JP6

pins 1-2 (CARRIER_25MHz to CARRIER_25MHZ_S) on ISMNET, because the 25 MHz clock source

for the Ethernet PHYs is also used as the clock source for the whole system including EtherCAT IP

core in the Spartan-6 LX150T FPGA. Configure FMC IO voltage to 2.5V. You can optionally connect

the UART or the LX150T (JR1) to your PC (9600 baud, 8 bit data, 1 stop bit, no parity, no hardware

handshake). The LEDs D3 and D4 on the FMC ISMNET module are used as Link/Activity LEDs for the

two Ethernet ports. Push button SW2 on the LX150T is used as system reset input.

The Microblaze demo application performs the following tasks:

Accept any EtherCAT Slave State request (copying AL Control to AL Status register). Print state

changes via UART.

Copy output data from EtherCAT IP Core (0x1024) to GPIO for LEDs D7-D14 on the LX150T.

Copy output data from EtherCAT IP Core (0x1004) to GPIO for DIGILENT U15 on the ISMNET.

Print output data from the EtherCAT IP Core (0x1020-0x1023) via UART.

Copy input data from GPIO for push buttons SW3-SW5 on the LX150T to the EtherCAT IP Core

(0x1000).

Copy input data from GPIO for push buttons SW1-SW2 on the ISMNET module to the EtherCAT

IP Core (0x1002).

Copy input data from GPIO for DIP switches SW6 on the LX150T to the EtherCAT IP Core

(0x1001).

Copy input data from GPIO for DIP switches SW3 on the ISMNET module to the EtherCAT IP

Core (0x1003).

6.2.3

Implementation

1. Open Xilinx EDK

1. Open project:

2. Generate Bitstream (Menu Hardware

– Generate Bitstream). Result is the file "system.bit" in the

implementation folder of the EDK project. This configuration file only includes the hardware parts

of the design, without software for the processor.

3. Select menu Project

– Export hardware design to SDK…

4. Select Export & Launch SDK

5. In SDK, select menu File

– New – Xilinx C Project

6.

Enter a project name, and select project template “BECKHOFF EtherCAT LX150T”

7. Select Next, then Finish.

8. Wait until the projects are built automatically, or select menu Project

– Build All

9. Update Bitstream with application image and download to FPGA by selecting menu Xilinx Tools

–

Program FPGA

Result is the file “download.bit” (= “system.bit” + “

folder of the EDK project.