BECKHOFF EtherCAT IP Core for Xilinx FPGAs v2.04e User Manual

Page 29

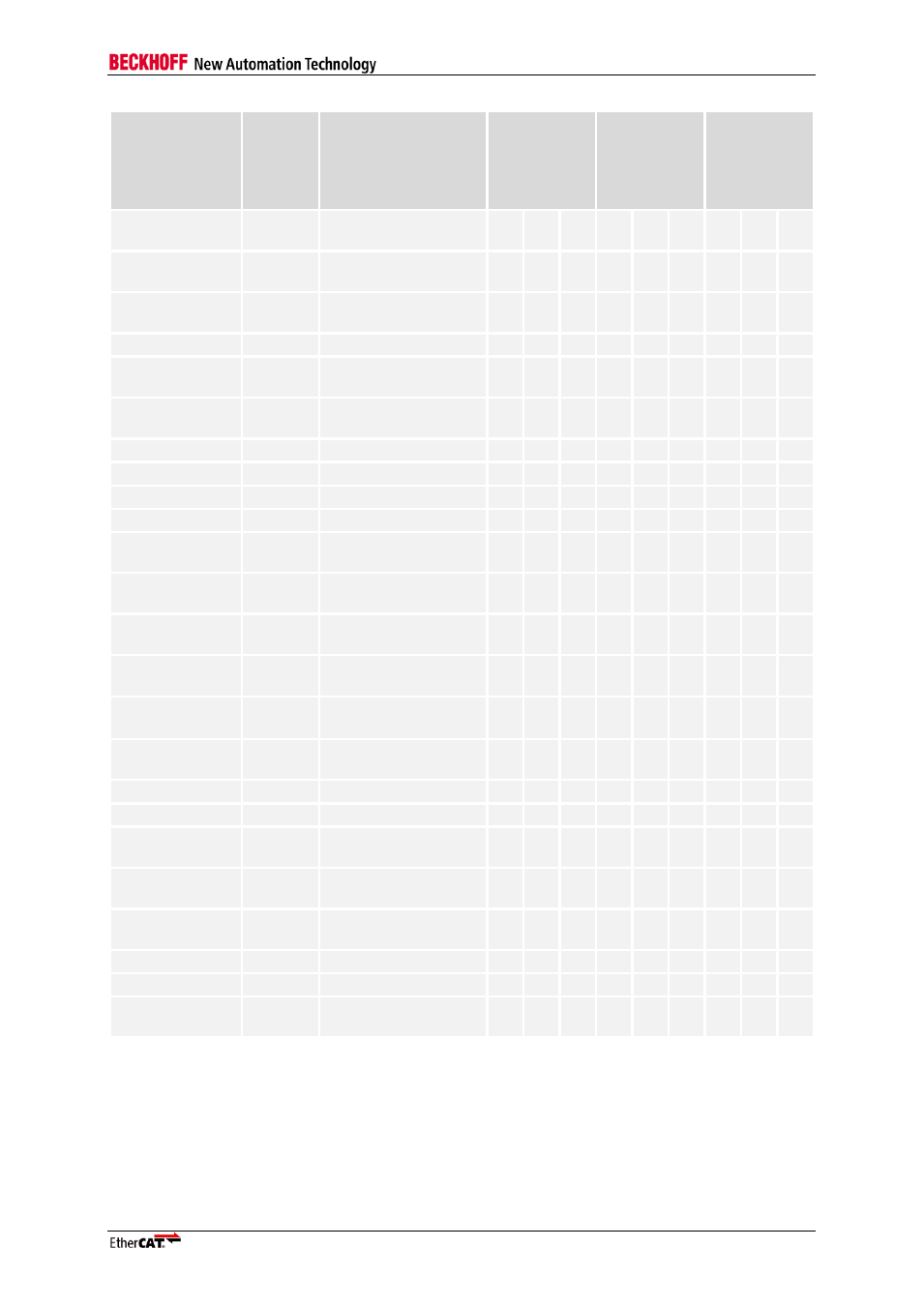

Features and Registers

Slave Controller

– IP Core for Xilinx FPGAs

III-17

Address

Length

(Byte)

Description

IP Core

V2.4.0-V2.4.4/

V2.04a-V2.04e

Register set

S

M

L

IP Core

V2.3.0-V2.3.2/

V2.03a-V2.03d

Register set

S

M

L

IP Core

V2.2.1/V2.2.0/

V2.02a

Register set

S

M

L

0x0920:0x0935

24

DC

– Time Loop

Control Unit

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x0936

1

DC

– Receive Time

Latch mode

-

-

-

-

-

-

-

-

-

0x0980

1

DC

– Cyclic Unit

Control

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x0981

1

DC

– Activation

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x0982:0x0983

2

DC

– Pulse length of

SyncSignals

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x0984

1

DC

– Activation

Status

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x098E:0x09A7

26

DC

– SYNC Out Unit

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09A8

1

DC

– Latch0 Control

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09A9

1

DC

– Latch1 Control

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09AE

1

DC

– Latch0 Status

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09B0:0x09B7

8

DC

– Latch0 Positive

Edge

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09B8:0x09BF

8

DC

– Latch0

Negative Edge

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09C0:0x09C7

8

DC

– Latch1 Positive

Edge

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09C7:0x09CF

8

DC

– Latch1

Negative Edge

dc

dc

dc

dc

dc

dc

dc

dc

dc

0x09F0:0x09F3

0x09F8:0x09FF

12

DC

– SyncManager

Event Times

c

c

c

c

c

c

c

c

c

0x0E00:0x0E03

4

Power-On Values

(Bits)

-

-

-

-

-

-

-

-

-

0x0E00:0x0E07

8

Product ID

x

x

x

x

x

x

x

x

x

0x0E08:0x0E0F

8

Vendor ID

x

x

x

x

x

x

x

x

x

0x0F00:0x0F03

4

Digital I/O Output

Data

io

io

io

io

io

io

io

io

io

0x0F10:0x0F17

8

General Purpose

Outputs [Byte]

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0x0F18:0x0F1F

8

General Purpose

Inputs [Byte]

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0-

8

0x0F80:0x0FFF

128

User RAM

x

x

x

x

x

x

x

x

x

0x1000:0x1003

4

Digital I/O Input Data

io

io

io

io

io

io

io

io

io

0x1000 ff.

Process Data RAM

[Kbyte]

1-

60

1-

60

1-

60

1-

60

1-

60

1-

60

1-

60

1-

60

1-

60