6 pci express, 7 sata, 6 pci express 4.7 sata – Artesyn iVPX7225 Installation and Use (April 2015) User Manual

Page 72: Figure 4-3, Slt3-pay-1f1f2u-14.2.4 slot profile, Functional description

Functional Description

iVPX7225 Installation and Use (6806800S11C)

53

4.6

PCI Express

iVPX7225 provides two x4 PCI-E Gen 2 ports to the VPX backplane. One of which can be

configured as Non-Transparent Bridge.

A PLX PEX8617 PCIe Gen2, 5.0 GT/s switch is used to implement the VPX dual FAT Pipe. CPU

PEG Port 0 (lanes 0-7) is the host port routed to the PEX. From the factory, PEX Port 3 is

configured as a Non-Transparent Bridge while PEX Port 1 is configured as a Transparent bridge.

The configuration is determined via EEPROM. PEX Port 1 is routed as PCIE_FP1/DP01 on P1.

PEX Port 3 is routed as PCIE_FP2/DP02 on P1.

4.7

SATA

iVPX7225 provides two SATA Gen 3 (up to 6Gbit/s) ports and one SATA Gen 2 (up to 3Gbit/s)

port routed to the VPX backplane P1 connector and another SATA Gen 2 (up to 3Gbit/s) port

routed to the XMC.

RTM planar SATA connector, J5 supports SATA Gen2. RTM Front panel e-SATA connector

supports SATA Gen2 and SATA Gen 3. The RTM planar SATA connector J4 is Gen3 capable.

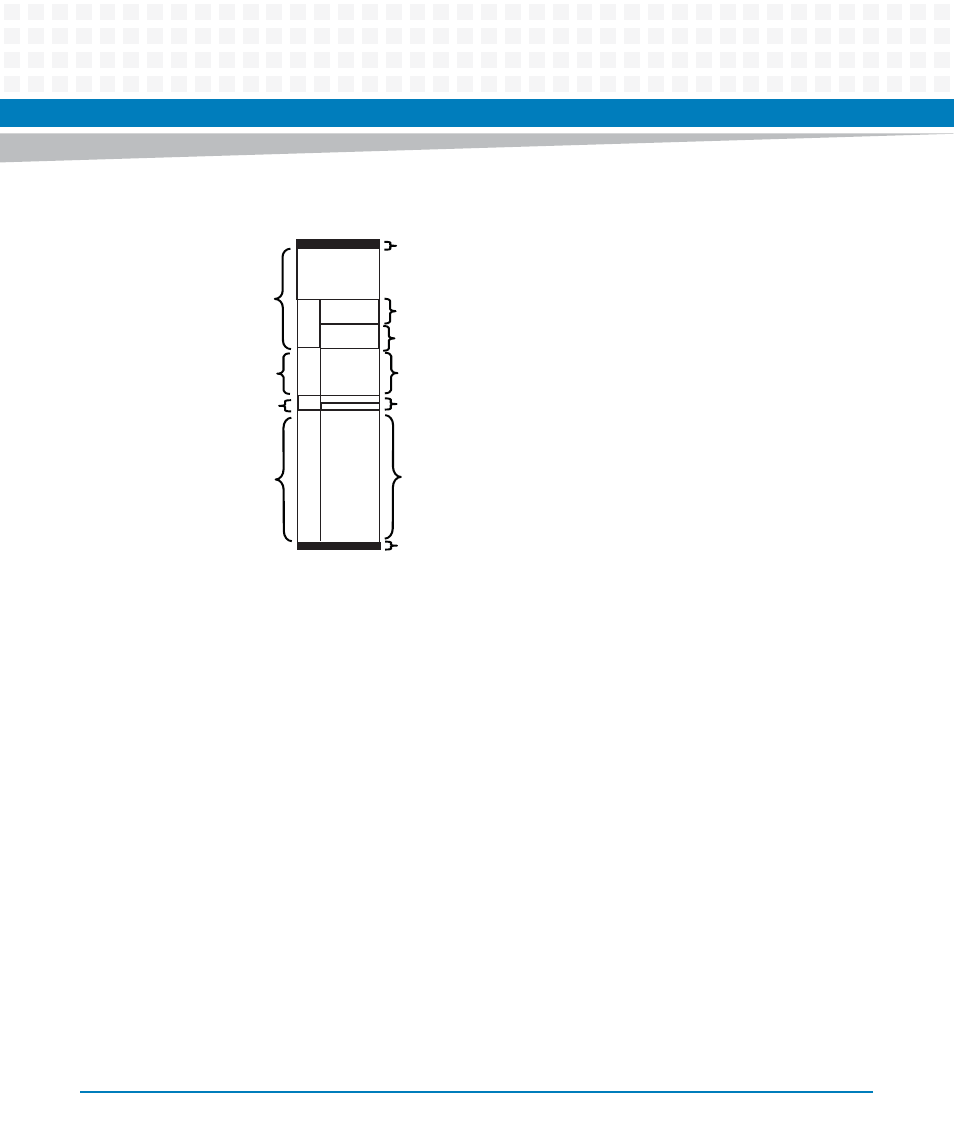

Figure 4-3

SLT3-PAY-1F1F2U-14.2.4 Slot Profile

Key

Data Plane - 1 Fat Pipe

User Defined

User Defined

Key

S

E

User Defined

Utility Plane

User Defined

Utility Plane

SE

P0/J0

Control Plane - 2 Ultra-Thin Pipes

Diff

P1/J1

S

E

Diff

P2/J2

Expansion Plane - 8 pairs