S:17ćs:27 – Rockwell Automation 1785-L20C_L40C, D17856.5.14 ControlNet PLC-5 Programmable Controllers User Manual User Manual

Page 86

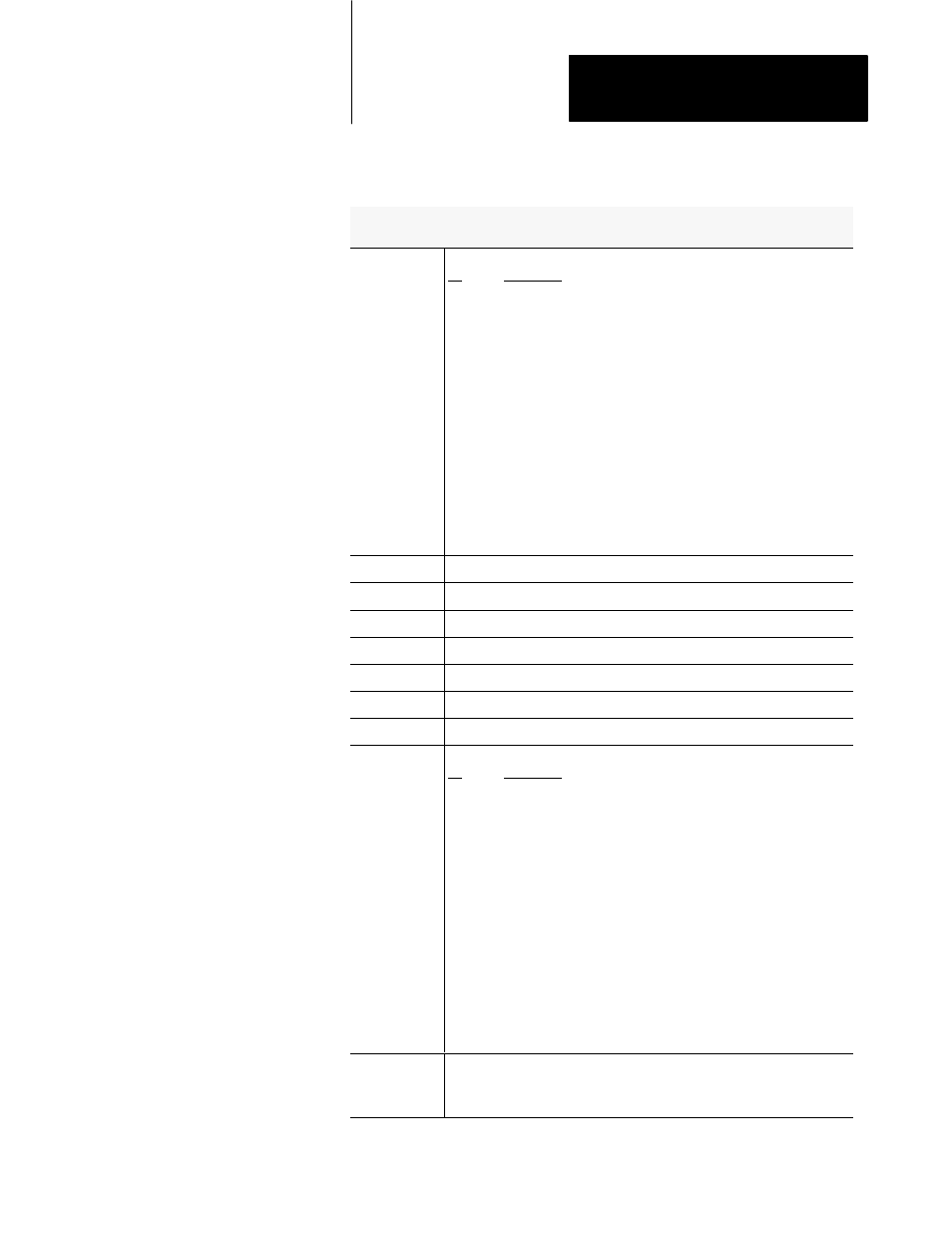

Processor Status File

Appendix B

B-5

This word of

the status file:

Stores:

S:17

Minor fault (word 2)

Bit

Description

0

BT queue full to remote I/O

1

queue fullĊchannel 1A

2

queue fullĊchannel 1B

3

queue fullĊchannel 2A

4

queue fullĊchannel 2B

5

no modem on serial port

6

remote I/O rack in local rack table; or, remote I/O rack is greater

than the image size

7

plug firmware revision does not match processor firmware revision

8

ASCII instruction error

9

duplicate network address

10

DF1 master poll list error

11

protectedĆprocessor dataĆtable element violation

12

protectedĆprocessor file violation

13

using all 32 ControlNet MSGs

14

using all 32 ControlNet 1771 READ and/or 1771 WRITE CIOs

15

using all 8 ControlNet Flex I/O CIOs

S:18

Processor clock year

S:19

Processor clock month

S:20

Processor clock day

S:21

Processor clock hour

S:22

Processor clock minute

S:23

Processor clock second

S:24

Indexed addressing offset

S:26

User control bits

Bit

Description

0

Restart/continuous SFC: when reset, processor restarts at first

step in SFC.

When set, processor continues with active step after power loss

or change to Run

1

StartĆup protection after power loss: when reset, no protection.

When set, processor executes fault routine at powerĆup

(sets word 11, bit 5).

2

Define the address of the local rack: when reset, local rack

address is 0. When set, local rack address is 1.

3

Set complementary I/O: when reset, complementary I/O is not

enabled. When set, complementary I/O is enabled.

4

Local block transfer compatibility bit: when reset, normal

operation. When set, eliminates frequent checksum errors to

certain BT modules.

5

When set (1), delay adapter channel response by 1 s for

compatibility with PLCĆ3 scanners. When reset (0), operate in

normal response time.

S:27

Rack control bits:

•

low 8 bitsĊI/O rack inhibit bits for racks 0Ć7

•

high 8 bitsĊI/O rack reset bits for racks 0Ć7

S:17ĆS:27