6 status bits, Status bits, Process data transfer – Lenze EMF2133IB User Manual

Page 76

Process data transfer

DRIVECOM control

Status bits

l

76

EDSMF2133IB EN 5.0

7.2.6

Status bits

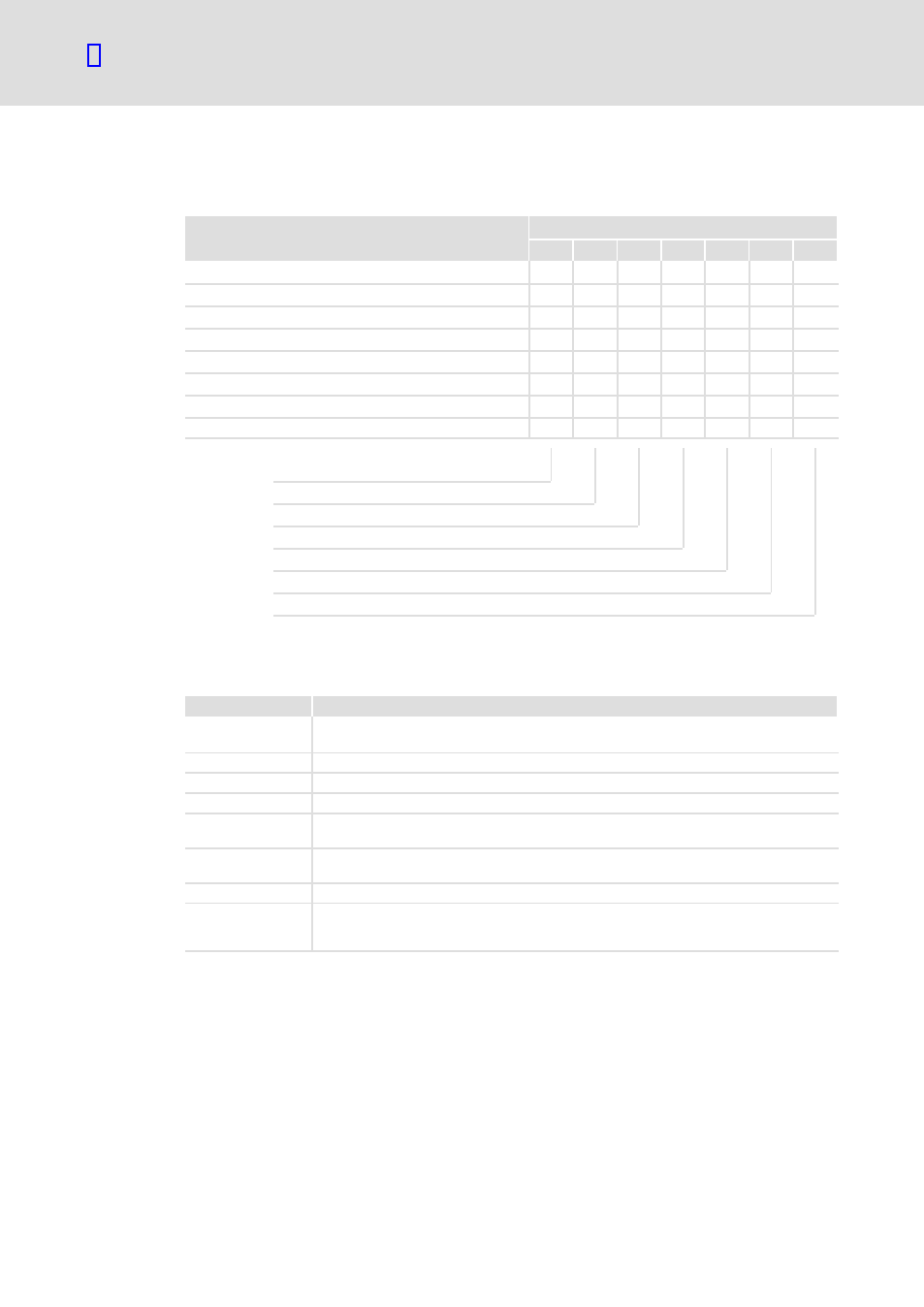

The current device status is clearly coded in bits 0 ... 6 of the status word:

Device status

Bits of the status word

6

5

4

3

2

1

0

NOT READY TO START

0

0

0

0

0

SWITCH−ON INHIBIT

1

0

0

0

0

READY TO START

0

1

0

0

0

1

SWITCHED ON

0

1

0

0

1

1

OPERATION ENABLED

0

1

0

1

1

1

FAULT

0

1

0

0

0

FAULT REACTION ACTIVE

0

1

1

1

1

QUICK STOP ACTIVE

0

0

0

1

1

1

Switch−on inhibit

Quick stop

Voltage inhibit

Fault

Operation enabled

Switched on

Ready to start

0:

Bit status is 0

1:

Bit status is 1

Empty:

Any bit status, no influence

Status

Description

NOT READY TO

START

During initialisation, the controller is not yet ready for operation. Afterwards it

automatically switches to the "READY TO START" device status.

SWITCH−ON INHIBIT The controller is inhibited and waits for command 2 (standstill).

READY TO START

The controller is inhibited and waits for command 3 (switch on).

SWITCHED ON

The controller is inhibited and waits for command 4 (enable operation).

OPERATION

ENABLED

The controller is enabled. In this device status the pulse inhibit can be set automatically.

FAULT REACTION

ACTIVE

A fault (TRIP) was recognised and a time−based fault−dependent response has been

initiated.

FAULT

The controller is in the "FAULT" (TRIP) device status.

QUICK STOP ACTIVE The "quick stop" (QSP) command was given in the device status "OPERATION ENABLED". A

controlled deceleration (quick stop ramp) is executed. After deceleration the device

changes automatically to the state "SWITCH−ON INHIBIT".