Rainbow Electronics DS26504 User Manual

Page 54

DS26504 T1/E1/J1/64KCC BITS Element

54 of 128

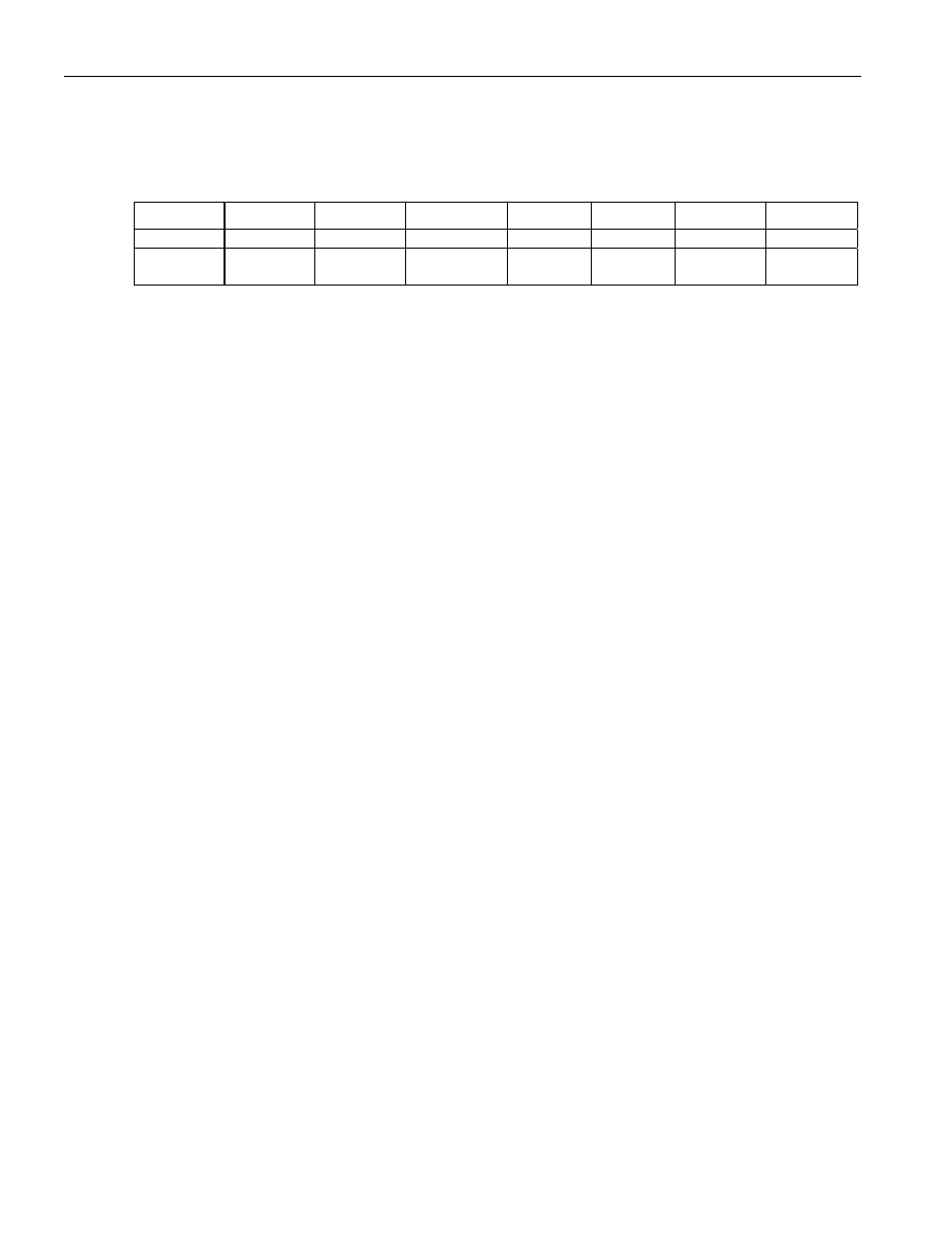

Register Name:

IOCR2

Register Description:

I/O Configuration Register 2

Register Address:

02h

Bit

# 7 6 5 4 3 2 1 0

Name

RCLKINV TCLKINV RS_8KINV

TS_8K_4INV

— —

TPCOE

RPCOE

Default

0 0 0 0 0 0 0 0

HW

Mode

0 0 0 0 0 0 0 0

Bit 0: Receive Payload Clock Output Enable (RPCOE). Setting this bit enables a gapped receive clock at the RCLK pin. In

E1 mode, the clock is gapped during TS0 and TS16. In T1 mode, the clock is gapped during the F-Bit. Note: This function is

only available in T1 or E1 mode.

Bit 1: Transmit Payload Clock Output Enable (TPCOE). Setting this bit enables a gapped transmit clock at the TCLKO

pin. In E1 mode, the clock is gapped during TS0 and TS16. In T1 mode, the clock is gapped during the F-Bit. Note: This

function is only available in T1 or E1 mode.

Bits 2 and 3: Unused, must be set = 0 for proper operation.

Bit 4: TS_8K_4 Invert (TS_8K_4INV)

0 = no inversion

1 = invert

Bit 5: RS_8K Invert (RS_8KINV)

0 = no inversion

1 = invert

Bit 6: TCLK Invert (TCLKINV)

0 = no inversion

1 = invert

Bit 7: RCLK Invert (RCLKINV)

0 = no inversion

1 = invert