Rainbow Electronics DS26504 User Manual

Page 86

DS26504 T1/E1/J1/64KCC BITS Element

86 of 128

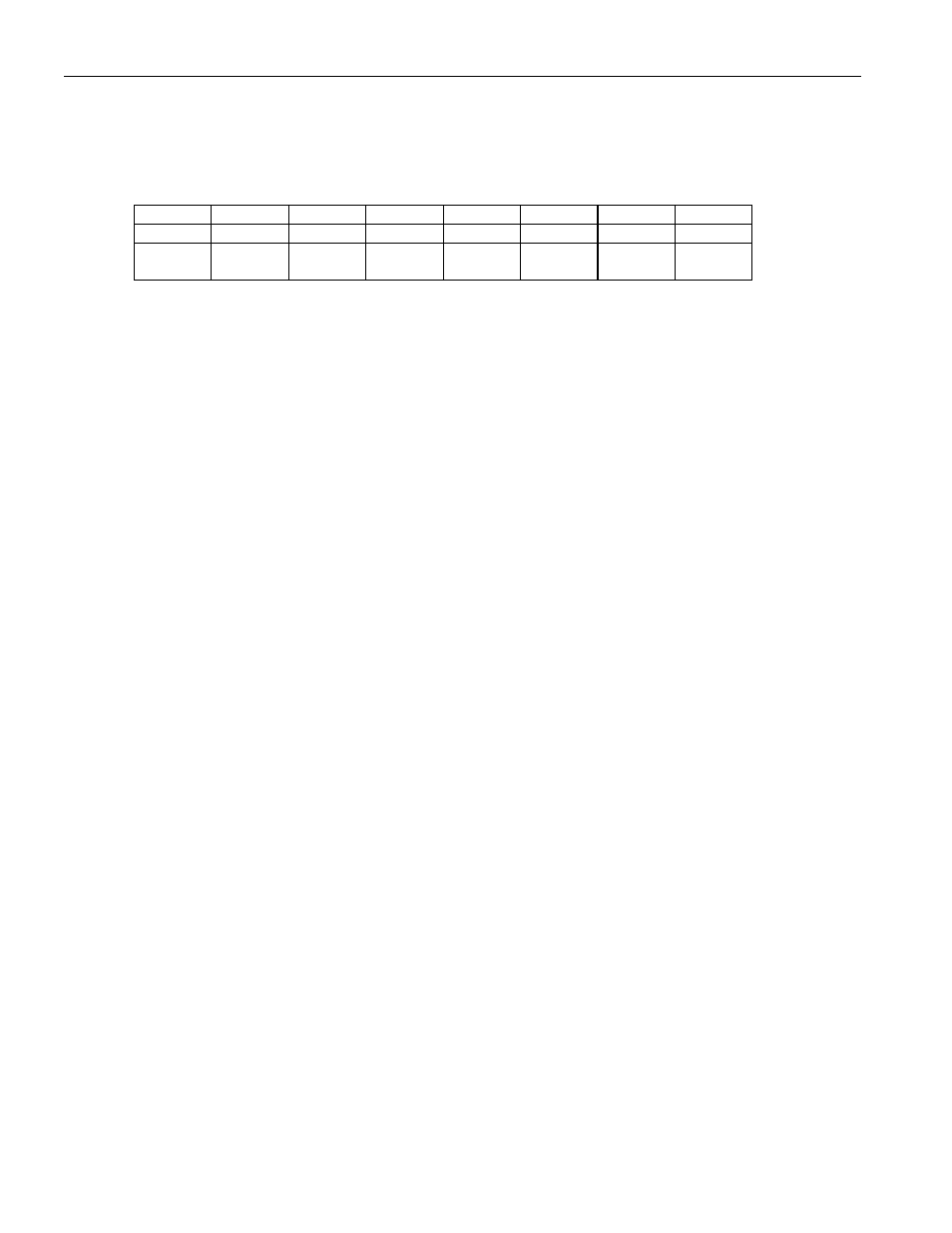

Register Name:

LIC2

Register Description:

Line Interface Control 2

Register Address:

31h

Bit

# 7 6 5 4 3 2 1 0

Name JACKS1

LIRST IBPV TAIS

JACKS0

RCCFE

SCLD CLDS

Default

0 0 0 0 0 0 0 0

HW

Mode

0 0 0

TAIS

PIN 10

JACKS0

PIN 46

0 0 0

Bit 0: Custom Line-Driver Select (CLDS). Setting this bit to a one redefines the operation of the transmit line driver. When

this bit is set to a one and LIC1.5 = LIC1.6 = LIC1.7 = 0, the device generates a square wave at the TTIP and TRING outputs

instead of a normal waveform. When this bit is set to a one and LIC1.5 = LIC1.6 = LIC1.7

¹ 0, the device forces TTIP and

TRING outputs to become open-drain drivers instead of their normal push-pull operation. This bit should be set to zero for

normal operation of the device.

Bit 1: Short Circuit Limit Disable (in E1 mode) (SCLD). Controls the 50mA (RMS) current limiter.

0 = enable 50mA current limiter

1 = disable 50mA current limiter

Bit 2: Receive Composite Clock Filter Enable (RCCFE) (64KCC mode only).

Setting this bit enables the PLL filter on the

received 64kHz composite clock. Note: The 8kHz and 400Hz output are not filtered.

0 = Receive Composite Clock Filter disabled

1 = Receive Composite Clock Filter enabled

Bit 3: Jitter Attenuator Mux (JACKS0). This bit, along with JACKS1 (LIC2.3), MPS0 (LIC4.6), and MPS1 (LIC4.7),

controls the source for JA CLOCK from the MCLK pin. Note: This bit must be configured even if the jitter attenuator is

disabled. The clock and data recovery engine also uses the JA CLOCK. Setting this bit enables the 12.8MHz to 2.048MHz

conversion PLL. See the table in the LIC4 register description for more details on setting up the JA CLOCK source.

Bit 4: Transmit Alarm Indication Signal (TAIS). In T1, E1, or J1 modes, this bit causes an all-ones pattern to be

transmitted.

0 = transmit an unframed all-ones code

1 = transmit data normally

In all 64KCC modes, this bit disables the BPV-encoded sub-rates.

0 = transmit all ones without BPVs

1 = transmit normal 64KCC

Bit 5: Insert BPV (IBPV). A zero-to-one transition on this bit causes a single BPV to be inserted into the transmit data

stream. Once this bit has been toggled from a zero to a one, the device waits for the next occurrence of three consecutive ones

to insert the BPV. This bit must be cleared and set again for a subsequent error to be inserted.

Bit 6: Line Interface Reset (LIRST). Setting this bit from a zero to a one initiates an internal reset that resets the clock

recovery state machine and recenters the jitter attenuator. Normally this bit is only toggled on power-up. Must be cleared and

set again for a subsequent reset.

Bit 7: Jitter Attenuator Clock Select 1 (JACKS1). This bit, along with JACKS0 (LIC2.3), MPS0 (LIC4.6), and MPS1

(LIC4.7), controls the source for JA CLOCK from the MCLK pin. Note: This bit must be configured even if the jitter

attenuator is disabled. The clock and data recovery engine also uses the JA CLOCK. Setting this bit enables the 12.8MHz to

2.048MHz conversion PLL. See the table in the LIC4 register description for more details on setting up the JA CLOCK source.

0 = 12.8MHz to 2.048MHz PLL bypassed

1 = 12.8MHz to 2.048MHz PLL enabled