Information registers, Interrupt information registers, Nformation – Rainbow Electronics DS26504 User Manual

Page 38: Egisters, Nterrupt, 6 information registers, 7 interrupt information registers

DS26504 T1/E1/J1/64KCC BITS Element

38 of 128

individually poll certain bits without disturbing the other bits in the register. This operation is key in

controlling the DS26504 with higher-order languages.

Status register bits are divided into two groups: condition bits and event bits. Condition bits are typically

network conditions such as loss of frame or all-ones detect. Event bits are typically markers such as the

one-second timer. Each status register bit is labeled as a condition or event bit. Some of the status

registers have bits for both the detection of a condition and the clearance of the condition. For example,

SR2 has a bit that is set when the device goes into a loss-of-frame state (SR2.0, a condition bit) and a bit

that is set (SR2.4, an event bit) when the loss-of-frame condition clears (goes in sync). Some of the status

register bits (condition bits) do not have a separate bit for the “condition clear” event but rather the status

bit can produce interrupts on both edges, setting, and clearing. These bits are marked as “double interrupt

bits.” An interrupt is produced when the condition occurs and when it clears.

7.6 Information Registers

Information registers operate the same as status registers except they cannot cause interrupts. INFO3

register is a read-only register and it reports the status of the E1 synchronizer in real time. INFO3

information bits are not latched, and it is not necessary to precede a read of these bits with a write.

7.7 Interrupt Information Registers

The Interrupt Information Registers (IIRs) provide an indication of which Status Registers (SR1 to SR4)

are generating an interrupt. When an interrupt occurs, the host can read IIR to quickly identify which of

the four status registers are causing the interrupt.

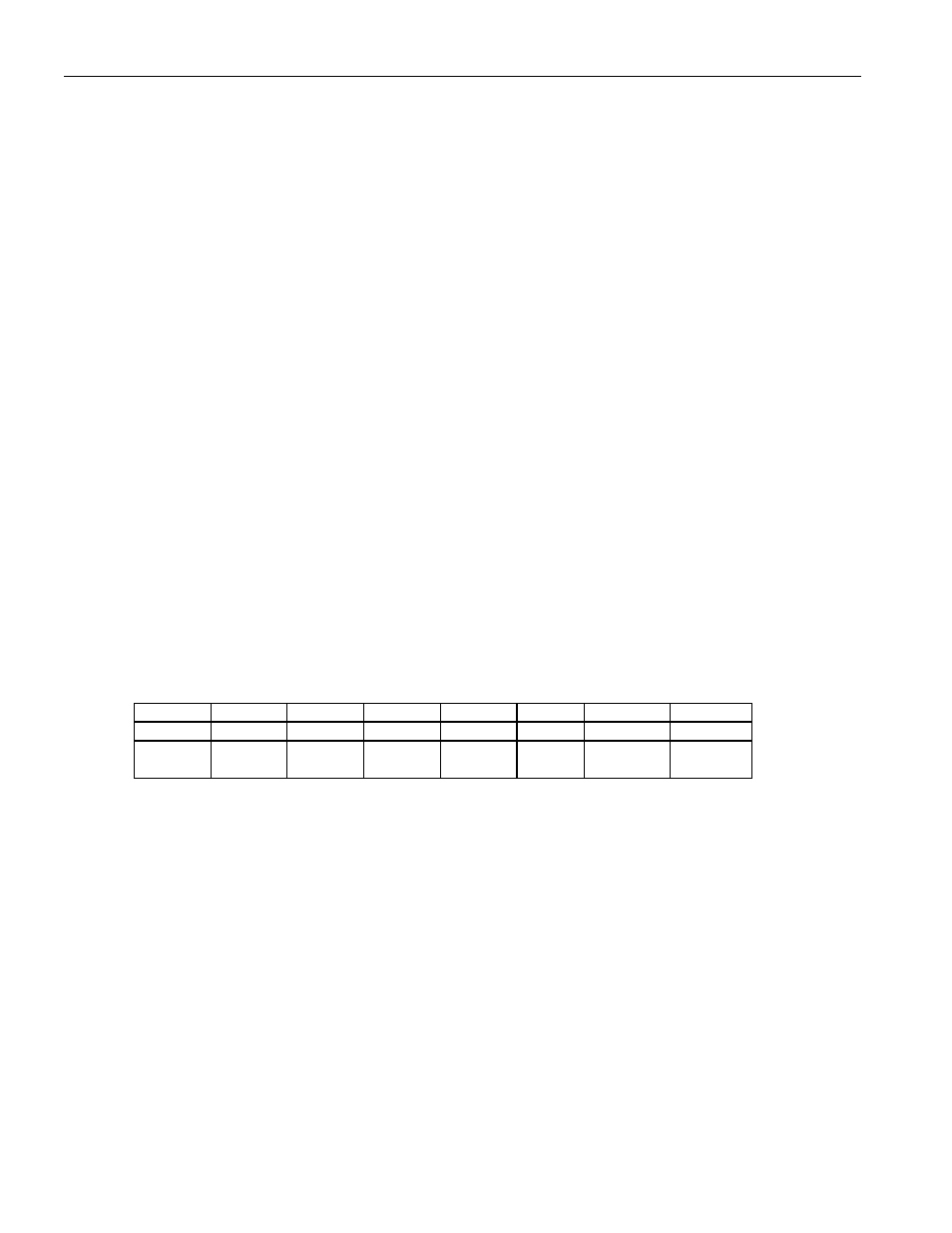

Register Name:

IIR

Register Description:

Interrupt Information Register

Register Address:

13h

Bit

# 7 6 5 4 3 2 1 0

Name — — — — SR4

SR3

SR2 SR1

Default

0 0 0 0 0 0 0 0

HW

Mode

X X X X X X X X

Bit 0: Status Register 1 (SR1)

0 = Status Register 1 interrupt not active.

1 = Status Register 1 interrupt active.

Bit 1: Status Register 2 (SR2)

0 = Status Register 2 interrupt not active.

1 = Status Register 2 interrupt active.

Bit 2: Status Register 3 (SR3)

0 = Status Register 3 interrupt not active.

1 = Status Register 3 interrupt active.

Bit 3: Status Register 4 (SR4)

0 = Status Register 4 interrupt not active.

1 = Status Register 4 interrupt active.

Bits 4 to 7: Unused