Processor interface, Parallel port functional description, Spi serial port interface functional description – Rainbow Electronics DS26504 User Manual

Page 30: Clock phase and polarity, Bit order, Control byte, Burst mode, Arallel, Unctional, Escription

DS26504 T1/E1/J1/64KCC BITS Element

30 of 128

7. PROCESSOR INTERFACE

The DS26504 is controlled via a nonmultiplexed (BIS[1:0] = 01) or a multiplexed (BIS[1:0] = 00)

parallel bus. There is also a serial bus mode option, as well as a hardware mode of operation. The bus

interface type is selected by BIS1 and BIS0 as shown in

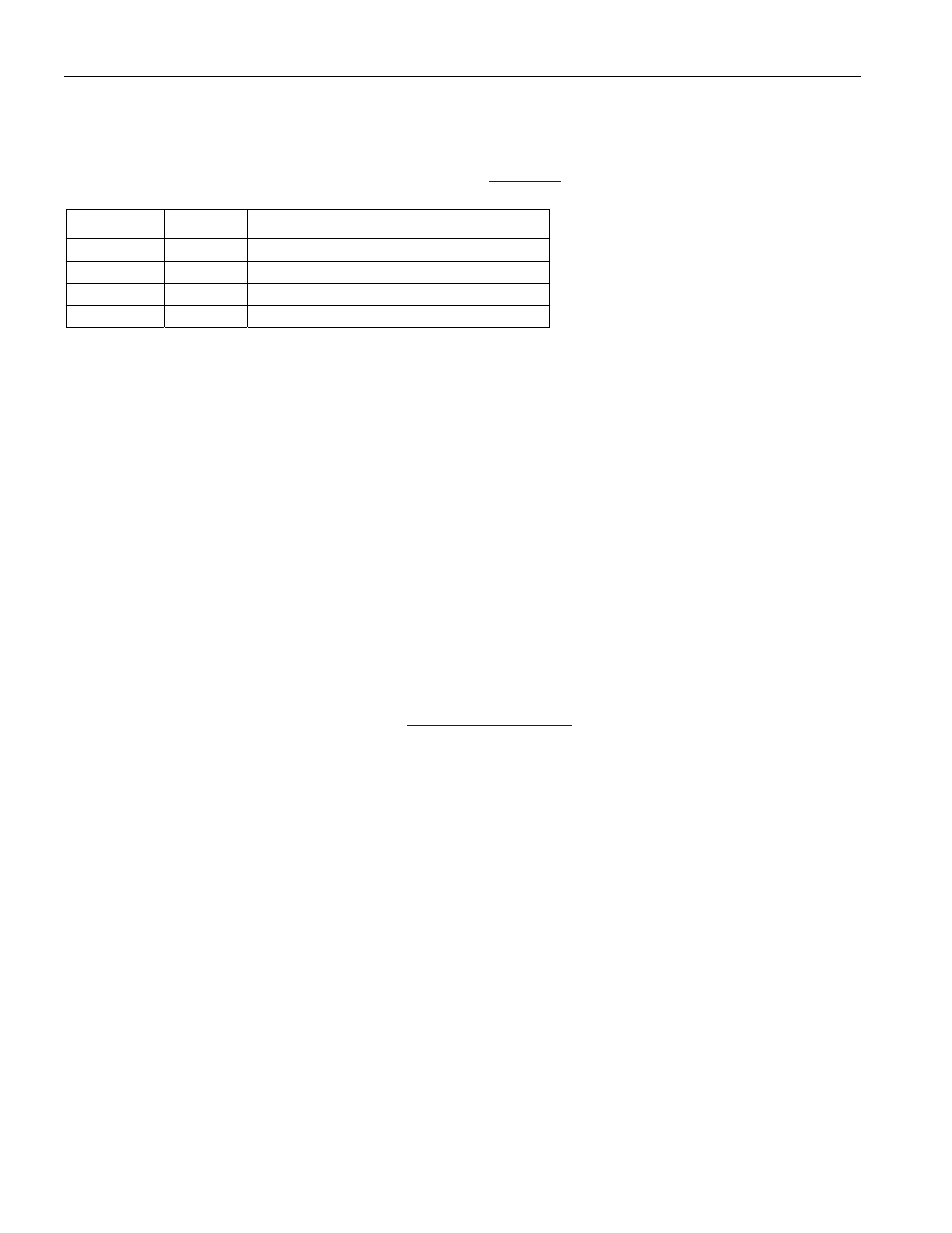

Table 7-1. Port Mode Select

BIS1 BIS0

PORT

MODE

0

0

Parallel Port Mode (Multiplexed)

0

1

Parallel Port Mode (Nonmultiplexed)

1

0

Serial Port Mode (SPI)

1 1

Hardware

Mode

7.1 Parallel Port Functional Description

In parallel mode, the DS26504 can operate with either Intel or Motorola bus timing configurations. If the

BTS pin is tied low, Intel timing will be selected; if tied high, Motorola timing will be selected. All

Motorola bus signals are listed in parentheses (). See the timing diagrams in the AC Electrical

Characteristics section for more details.

7.2 SPI Serial Port Interface Functional Description

A serial SPI bus interface is selected when the bus select is 10 (BIS[1:0] = 10). In this mode, a

master/slave relationship is enabled on the serial port with three signal lines (SCK, MOSI, and MISO)

and a chip select (

CS), with the DS26504 acting as the slave. Port read/write timing is not related to the

system read/write timing, thus allowing asynchronous, half-duplex operation. See the AC Electrical

Characteristics section for the AC timing characteristics of the serial port.

7.2.1 Clock Phase and Polarity

Clock Phase and Polarity are selected by the CPHA and CPOL pins. The slave device should always be

configured to match the bus master. See the

section for detailed functional timing

diagrams.

7.2.2 Bit Order

The most significant bit (MSB) of each byte is transmitted first.

7.2.3 Control Byte

The bus master will transmit two control bytes following a chip select to a slave device. The MSB will be

a R/

W bit (1 = read, 0 = write). The next 6 bits will be padded with zeros. The LSB of the first byte will

be A[7]. The second control byte will be the address bits (A[6:0]) of the target register, followed by a

Burst bit in the LSB position (1 = Burst, 0 = Nonburst).

7.2.4 Burst Mode

The last bit of the second control byte (LSB) is the Burst Mode bit. When the Burst bit is enabled (set to

1) and a read operation is performed, the register address is automatically incremented after the LSB of

the previous byte read to the next register address. Data will be available on the next clock edge following

the LSB of the previous byte read. When the Burst bit is enabled (set to 1) and a write operation is

performed, the register address will be automatically incremented to the next byte boundary following the

LSB of the previous register write, and 8 more data bits will be expected on the serial bus. Burst accesses