Table 9-2. e1 alarm criterion – Rainbow Electronics DS26504 User Manual

Page 49

DS26504 T1/E1/J1/64KCC BITS Element

49 of 128

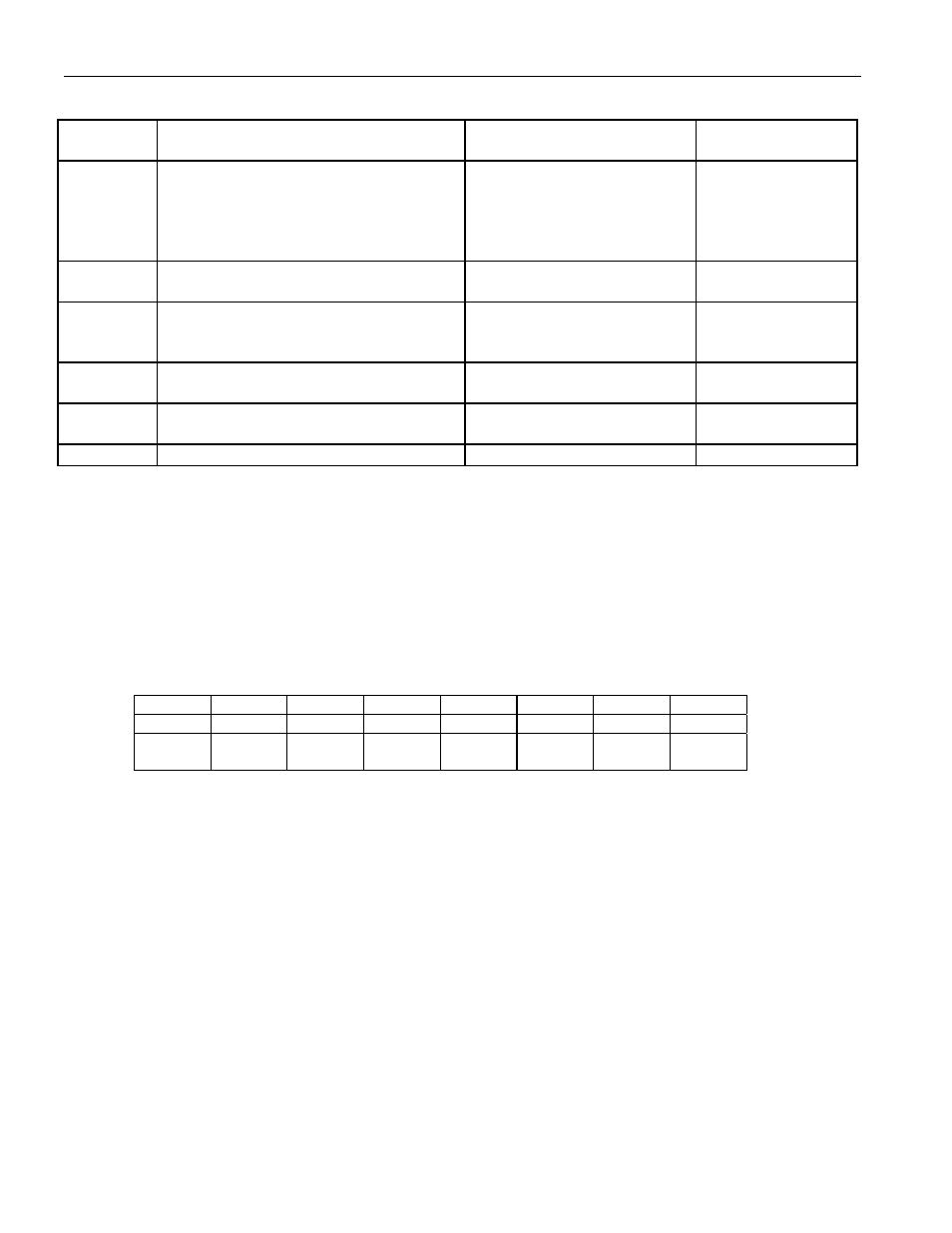

Table 9-2. E1 Alarm Criterion

ALARM

SET CRITERION

CLEAR CRITERION

ITU

SPEC.

RLOF

An RLOF condition exists on power-up

prior to initial synchronization, when a

resync criterion has been met, or when a

manual resync has been initiated via

E1RCR.0

— —

RLOS

255 or 2048 consecutive zeros received as

determined by E1RCR.0

In 255-bit times, at least 32

ones are received

G.775/G.962

RRA

Bit 3 of non-align frame set to one for

three consecutive occasions

Bit 3 of non-align frame set to

zero for three consecutive

occasions

O.162

2.1.4

RUA1

Fewer than three zeros in two frames (512

bits)

More than two zeros in two

frames (512 bits)

O.162

1.6.1.2

RDMA

Bit 6 of time slot 16 in frame 0 has been

set for two consecutive multiframes

—

V52LNK

Two out of three Sa7 bits are zero

—

G.965

Register Name:

IDR

Register Description:

Device Identification Register

Register Address:

10h

Bit

# 7 6 5 4 3 2 1 0

Name ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

Default

0 0 0 0 N N N N

HW

Mode

X X X X X X X X

Bits 0 to 3: Chip Revision Bits (ID0 to ID3). The lower four bits of the IDR are used to display the die revision of the chip.

ID0 is the LSB of a decimal code that represents the chip revision.

Bits 4 to 7: Device ID (ID4 to ID7). The upper four bits of the IDR are used to display the DS26504 ID. The DS26504 ID is

0010.

DS26502

=

0000

DS26503

=

0001

DS26504

=

0010