Line interface, Power, Nterface – Rainbow Electronics DS26504 User Manual

Page 21: Ower

DS26504 T1/E1/J1/64KCC BITS Element

21 of 128

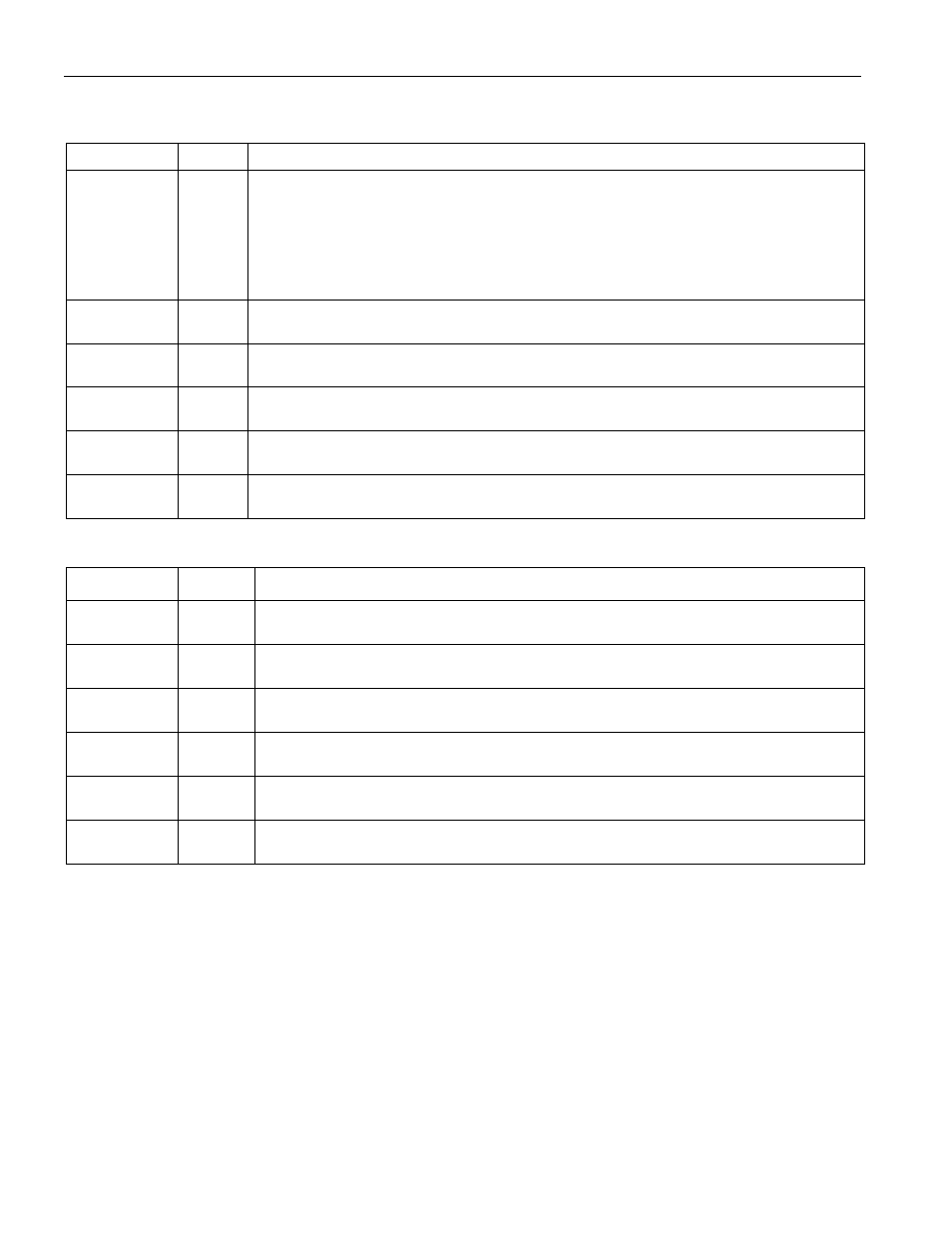

4.6 Line Interface

NAME TYPE

FUNCTION

MCLK I

Master Clock Input. A (50ppm) clock source. This clock is used internally for

both clock/data recovery and the jitter attenuator for both T1 and E1 modes. A

quartz crystal can be applied across MCLK and XTALD rather than the clock

source. The clock rate can be 16.384MHz, 8.192MHz, 4.096MHz, or

2.048MHz. When using the DS26504 in T1-only operation, a 1.544MHz

(50ppm) clock source can be used.

RTIP I

Receive Tip. Analog input for clock recovery circuitry. This pin connects via a

1:1 transformer to the network. See the Line Interface Unit section for details.

RRING I

Receive Ring. Analog input for clock recovery circuitry. This pin connects via

a 1:1 transformer to the network. See the Line Interface Unit section for details.

TTIP O

Transmit Tip. Analog line-driver output. This pin connects via a 1:2 step-up

transformer to the network. See the Line Interface Unit section for details.

TRING O

Transmit Ring. Analog line-driver output. This pin connects via a 1:2 step-up

transformer to the network. See the Line Interface Unit section for details.

THZE I

Transmit High-Impedance Enable. When high, TTIP and TRING will be

placed into a high-impedance state.

4.7 Power

NAME TYPE

FUNCTION

DVDD —

Digital Positive Supply. 3.3V ±5%. Should be tied to the RVDD and TVDD

pins.

RVDD —

Receive Analog Positive Supply. 3.3V ±5%. Should be tied to the DVDD and

TVDD pins.

TVDD —

Transmit Analog Positive Supply. 3.3V ±5%. Should be tied to the DVDD

and RVDD pins.

DVSS —

Digital Signal Ground. 0.0V. Should be tied to the RVSS and TVSS pins.

RVSS —

Receive Analog Signal Ground. 0.0V. Should be tied to the DVSS and TVSS

pins.

TVSS —

Transmit Analog Signal Ground. 0.0V. Should be tied to the DVSS and

RVSS pins.