Rainbow Electronics DS26504 User Manual

Page 42

DS26504 T1/E1/J1/64KCC BITS Element

42 of 128

Register Name:

T1TCR2

Register Description:

T1 Transmit Control Register 2

Register Address:

06h

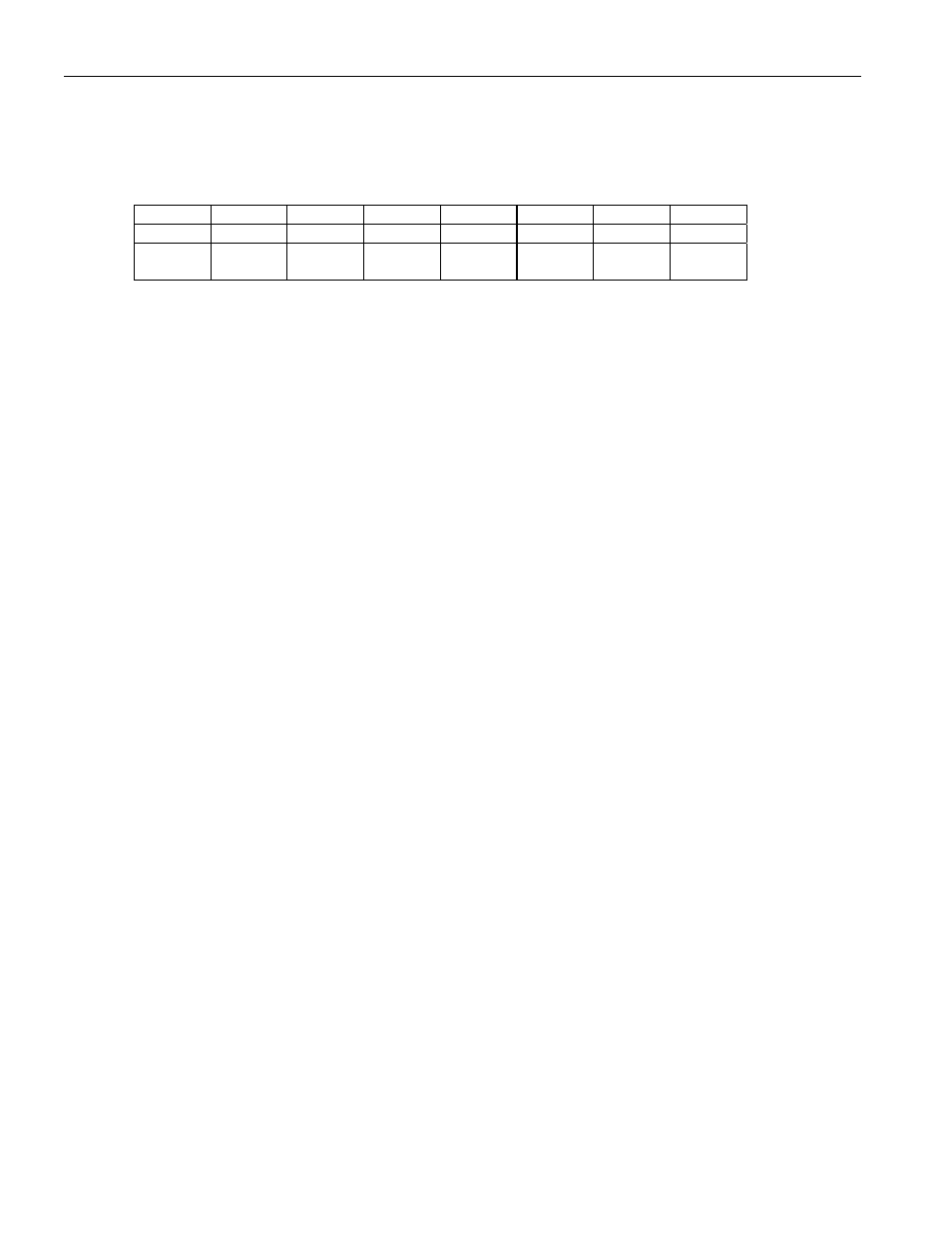

Bit

# 7 6 5 4 3 2 1 0

Name TB8ZS

TFSE — FBCT2

FBCT1

TD4YM — TB7ZS

Default

0 1 0 0 0 0 0 0

HW

Mode

HBE

PIN 55

1 0 0 0 0 0 0

Bit 0: Transmit-Side Bit 7 Zero-Suppression Enable (TB7ZS)

0 = no stuffing occurs

1 = bit 7 forced to a 1 in channels with all 0s

Bits 1 and 5: Unused, must be set = 0 for proper operation.

Bit 2: Transmit-Side D4 Yellow Alarm Select (TD4YM)

0 = 0s in bit 2 of all channels

1 = a 1 in the S-bit position of frame 12

Bit 3: F-Bit Corruption Type 1 (FBCT1). A low-to-high transition of this bit causes the next three consecutive Ft (D4

framing mode) or FPS (ESF framing mode) bits to be corrupted causing the remote end to experience a loss of frame (loss of

synchronization).

Bit 4: F-Bit Corruption Type 2 (FBCT2). Setting this bit high enables the corruption of one Ft (D4 framing mode) or FPS

(ESF framing mode) bit in every 128 Ft or FPS bits as long as the bit remains set.

Bit 6: Transmit Fs-Bit Insertion Enable (TFSE). Only set this bit to a 1 in D4 framing applications. Must be set to 1 to

source the Fs pattern from the TFDL register. In all other modes this bit must be set = 0.

0 = Fs-bit insertion disabled

1 = Fs-bit insertion enabled

Bit 7: Transmit B8ZS Enable (TB8ZS)

0 = B8ZS disabled

1 = B8ZS enabled