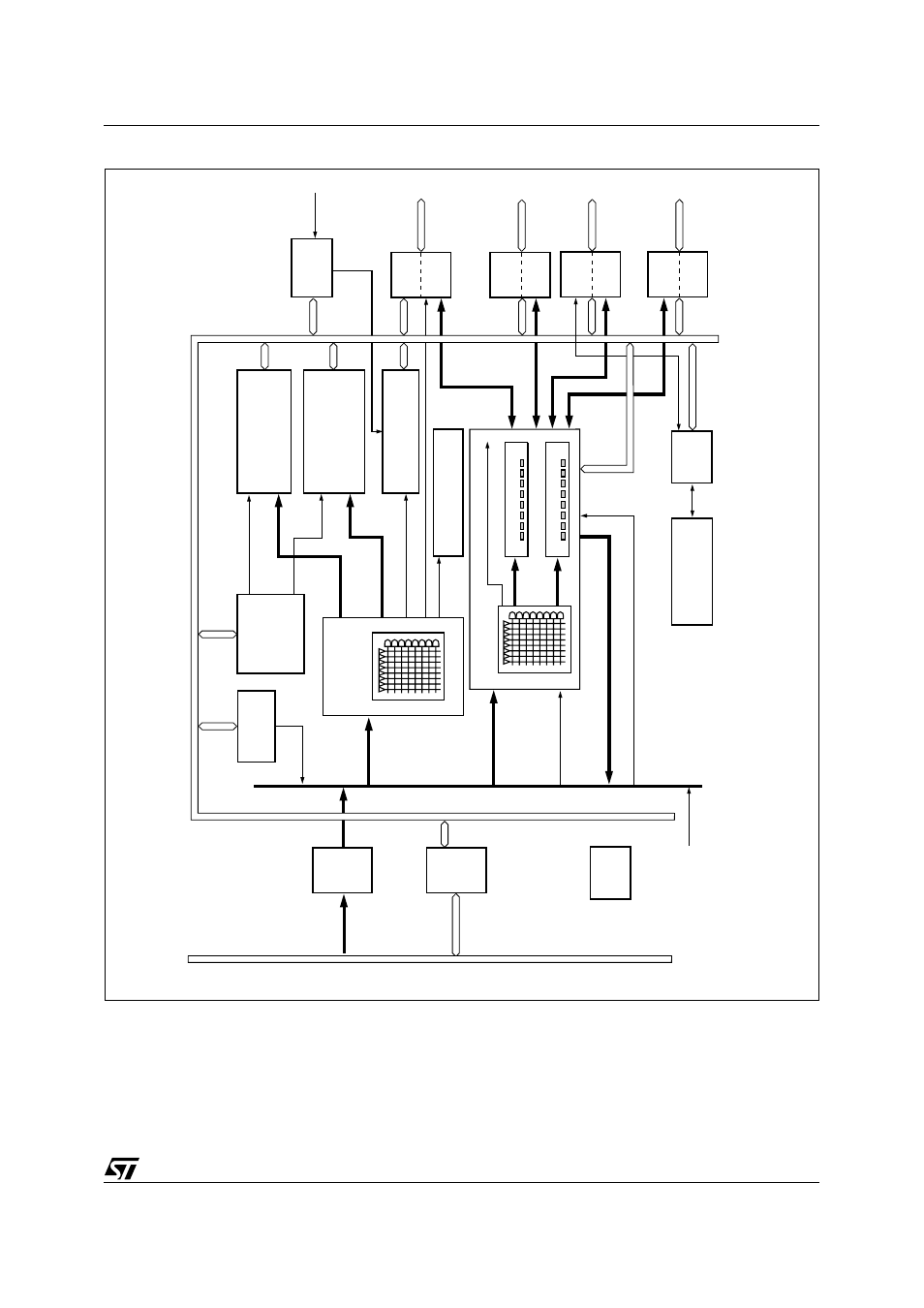

Figure 46. psd module block diagram – ST & T UPSD3212C User Manual

Page 89

89/163

uPSD3212A, uPSD3212C, uPSD3212CV

Figure 46. PSD MODULE Block Diagram

BUS

Interface

WR_, RD_,

PSEN_, ALE,

RESET_,

A0-A15

D0 – D7

CLKIN

(PD1)

CLKIN

CLKIN

PLD

INPUT

BUS

PROG.

PORT

PORT

A

PROG.

PORT

PORT

B

POWER

MANGMT

UNIT

512KBIT PRIMARY

FLASH MEMORY

8 SECTORS

VSTDBY

PA0 – PA7

PB0 – PB7

PROG.

PORT

PORT

C

PROG.

PORT

PORT

D

PC0 – PC7

PD1 – PD2

ADDRESS

/DATA

/CONTROL BUS

PORT A ,B & C

2 EXT CS TO PORT D

20 INPUT MACROCELLS

PORT A ,B & C

73

73

128KBIT SECONDARY

NON-VOLATILE MEMORY

(BOOT OR DATA)

2 SECTORS

16KBIT BATTERY

BACKUP SRAM

RUNTIME CONTROL

AND I/O REGISTERS

SRAM SELECT

PERIP I/O MODE SELECTS

MACROCELL FEEDBACK OR PORT INPUT

CSIOP

FLASH ISP CPLD

(CPLD)

16 OUTPUT MACROCELLS

FLASH DECODE

PLD

( DPLD

)

PLD, CONFIGURATION

& FLASH MEMORY

LOADER

JTAG

SERIAL

CHANNEL

( PC2

)

PAGE

REGISTER

EMBEDDED

ALGORITHM

SECTOR

SELECTS

SECTOR

SELECTS

GLOBAL

CONFIG. &

SECURITY

AI07431

8

BUS

Interface

8032 Bus