Watchdog timer, Table 33. description of the wdkey bits – ST & T UPSD3212C User Manual

Page 46

uPSD3212A, uPSD3212C, uPSD3212CV

46/163

WATCHDOG TIMER

The hardware Watchdog Timer (WDT) resets the

uPSD321x Devices when it overflows. The WDT is

intended as a recovery method in situations where

the CPU may be subjected to a software upset. To

prevent a system reset the timer must be reloaded

in time by the application software. If the processor

suffers a hardware/software malfunction, the soft-

ware will fail to reload the timer. This failure will re-

sult in a reset upon overflow thus preventing the

processor running out of control.

In the Idle Mode the watchdog timer and reset cir-

cuitry remain active. The WDT consists of a 22-bit

counter, the Watchdog Timer RESET (WDRST)

SFR and Watchdog Key Register (WDKEY).

Since the WDT is automatically enabled while the

processor is running. the user only needs to be

concerned with servicing it.

The 22-bit counter overflows when it reaches

4194304 (3FFFFFH). The WDT increments once

every machine cycle.

This means the user must reset the WDT at least

every 4194304 machine cycles (1.258 seconds at

40MHz). To reset the WDT the user must write a

value between 00-7EH to the WDRST register.

The value that is written to the WDRST is loaded

to the 7MSB of the 22-bit counter. This allows the

user to pre-loaded the counter to an initial value to

generate a flexible Watchdog time out period.

Writing a “00” to WDRST clears the counter.

The watchdog timer is controlled by the watchdog

key register, WDKEY. Only pattern 01010101

(=55H), disables the watchdog timer. The rest of

pattern combinations will keep the watchdog timer

enabled. This security key will prevent the watch-

dog timer from being terminated abnormally when

the function of the watchdog timer is needed.

In Idle Mode, the oscillator continues to run. To

prevent the WDT from resetting the processor

while in Idle, the user should always set up a timer

that will periodically exit Idle, service the WDT, and

re-enter Idle Mode.

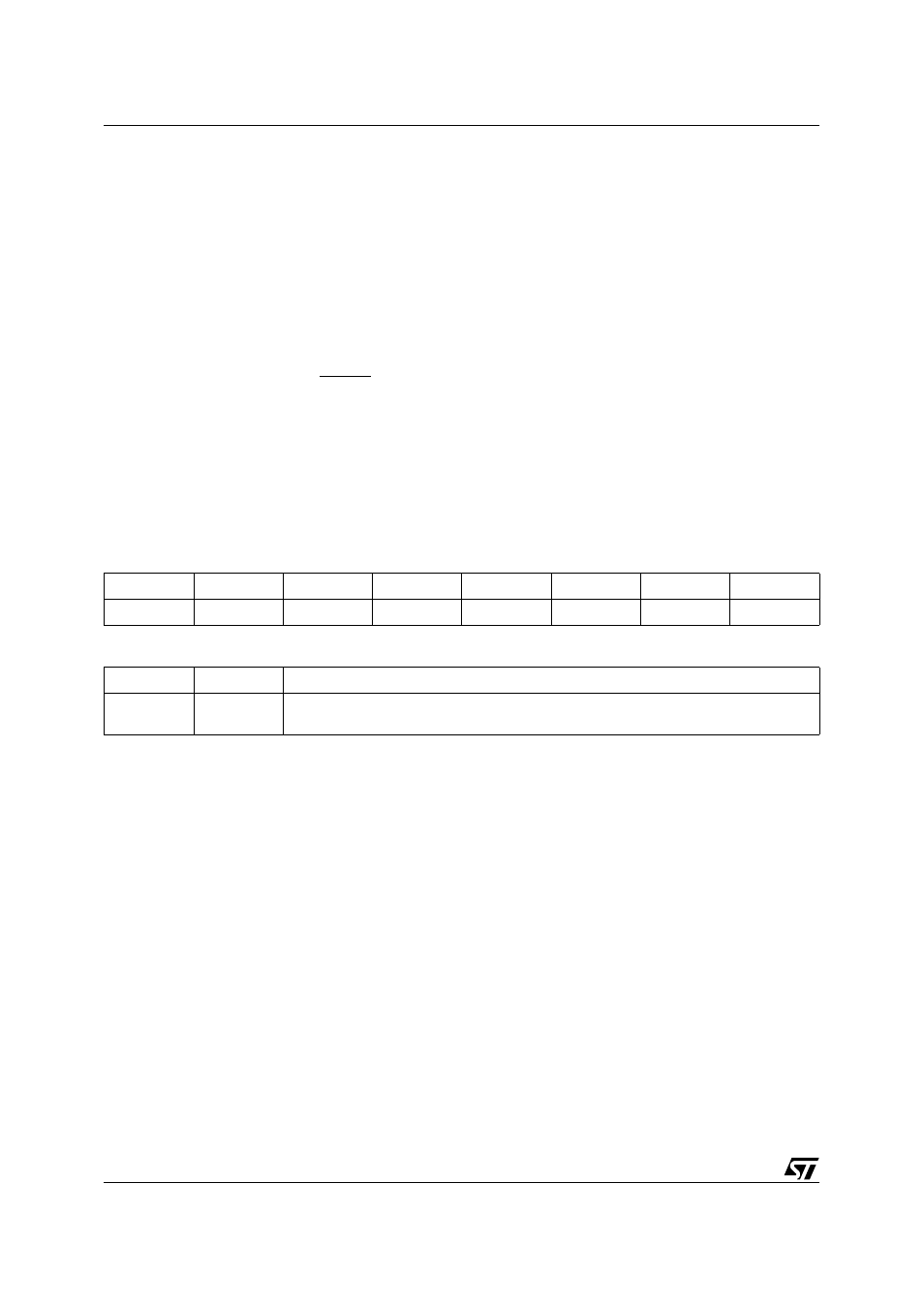

Table 32. Watchdog Timer Key Register (WDKEY: 0AEH)

Table 33. Description of the WDKEY Bits

7

6

5

4

3

2

1

0

WDKEY7

WDKEY6

WDKEY5

WDKEY4

WDKEY3

WDKEY2

WDKEY1

WDKEY0

Bit

Symbol

Function

7 to 0

WDKEY7 to

WDKEY0

Enable or disable Watchdog Timer.

01010101 (=55h): disable watchdog timer. Others: enable watchdog timer