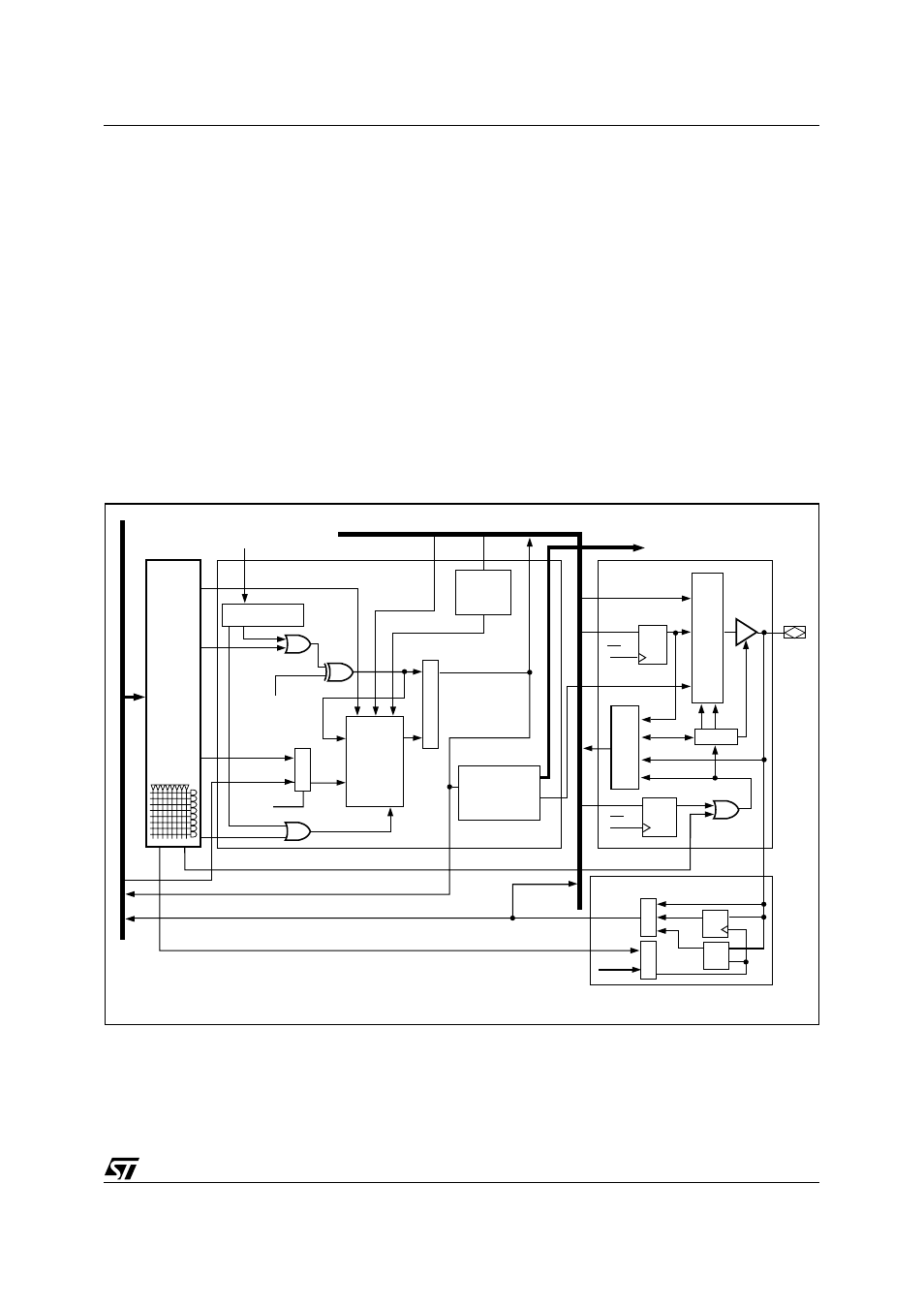

Complex pld (cpld), Figure 56. macrocell and i/o port, Complex pld – ST & T UPSD3212C User Manual

Page 109: 20 input macrocells (imc), 16 output macrocells (omc), Macrocell allocator, Product term allocator

109/163

uPSD3212A, uPSD3212C, uPSD3212CV

Complex PLD (CPLD)

The CPLD can be used to implement system logic

functions, such as loadable counters and shift reg-

isters, system mailboxes, handshaking protocols,

state machines, and random logic. The CPLD can

also be used to generate External Chip Select

(ECS1-ECS2), routed to Port D.

Although External Chip Select (ECS1-ECS2) can

be produced by any Output Macrocell (OMC),

these External Chip Select (ECS1-ECS2) on Port

D do not consume any Output Macrocells (OMC).

As shown in Figure

, the CPLD has the following

blocks:

■

20 Input Macrocells (IMC)

■

16 Output Macrocells (OMC)

■

Macrocell Allocator

■

Product Term Allocator

■

AND Array capable of generating up to 137

product terms

■

Four I/O Ports.

Each of the blocks are described in the sections

that follow.

The Input Macrocells (IMC) and Output Macrocells

(OMC) are connected to the PSD MODULE inter-

nal data bus and can be directly accessed by the

MCU. This enables the MCU software to load data

into the Output Macrocells (OMC) or read data

from both the Input and Output Macrocells (IMC

and OMC).

This feature allows efficient implementation of sys-

tem logic and eliminates the need to connect the

data bus to the AND Array as required in most

standard PLD macrocell architectures.

Figure 56. Macrocell and I/O Port

I/O PORTS

CPLD MACROCELLS

INPUT MACROCELLS

LATCHED

ADDRESS OUT

MUX

MUX

MUX

MUX

MUX

D

D

Q

Q

Q

G

D

Q D

WR

WR

PDR

DATA

PRODUCT TERM

ALLOCATOR

DIR

REG.

SELECT

INPUT

PRODUCT TERMS

FROM OTHER

MACROCELLS

POLARITY

SELECT

UP TO 10

PRODUCT TERMS

CLOCK

SELECT

PR

DI LD

D/T

CK

CL

Q

D/T/JK FF

SELECT

PT CLEAR

PT

CLOCK

GLOBAL

CLOCK

PT OUTPUT ENABLE (OE)

MACROCELL FEEDBACK

I/O PORT INPUT

ALE

PT INPUT LATCH GATE/CLOCK

MCU LOAD

PT PRESET

MCU DATA IN

COMB.

/REG

SELECT

MACROCELL

TO

I/O PORT

ALLOC.

CPLD

OUTPUT

TO OTHER I/O PORTS

PLD INPUT BUS

PLD INPUT BUS

MCU ADDRESS / DATA BUS

MACROCELL

OUT TO

MCU

DATA

LOAD

CONTROL

AND ARRAY

CPLD OUTPUT

I/O PIN

AI06602