Table 20. description of the ie bits, Table 21. description of the iea bits, Table 22. description of the ip bits – ST & T UPSD3212C User Manual

Page 37

37/163

uPSD3212A, uPSD3212C, uPSD3212CV

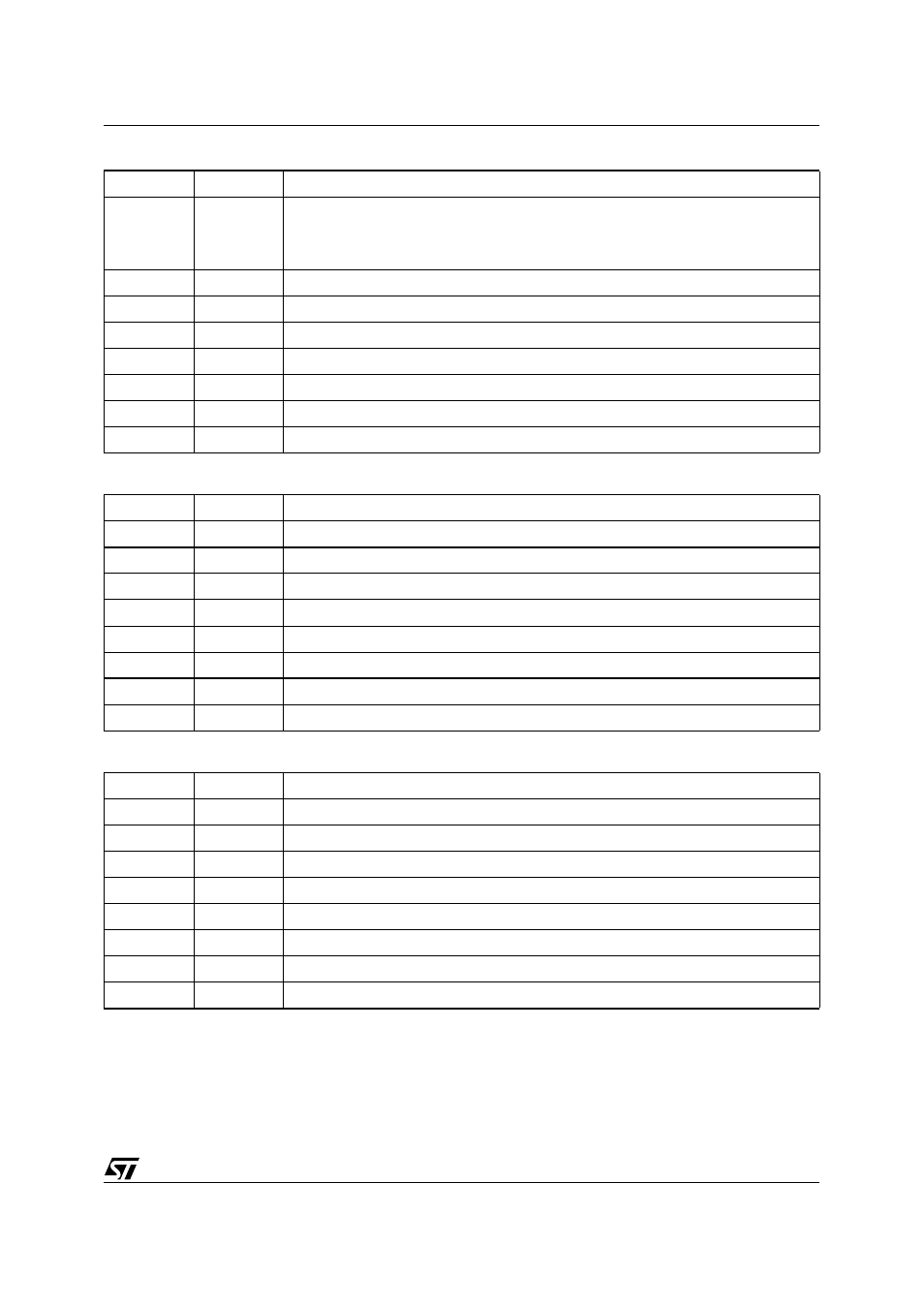

Table 20. Description of the IE Bits.

Table 21. Description of the IEA Bits

Table 22. Description of the IP Bits

Bit

Symbol

Function

7

EA

Disable all interrupts:

0: no interrupt with be acknowledged

1: each interrupt source is individually enabled or disabled by setting or clearing its

enable bit

6

—

Reserved

5

ET2

Enable Timer 2 Interrupt

4

ES

Enable USART Interrupt

3

ET1

Enable Timer 1 Interrupt

2

EX1

Enable External Interrupt (Int1)

1

ET0

Enable Timer 0 Interrupt

0

EX0

Enable External Interrupt (Int0)

Bit

Symbol

Function

7

—

Not used

6

—

Not used

5

—

Not used

4

ES2

Enable 2nd USART Interrupt

3

—

Not used

2

—

Not used

1

EI2C

Enable I²C Interrupt

0

EUSB

Enable USB Interrupt

Bit

Symbol

Function

7

—

Reserved

6

—

Reserved

5

PT2

Timer 2 Interrupt priority level

4

PS

USART Interrupt priority level

3

PT1

Timer 1 Interrupt priority level

2

PX1

External Interrupt (Int1) priority level

1

PT0

Timer 0 Interrupt priority level

0

PX0

External Interrupt (Int0) priority level