Table 46. adc sfr memory map, Table 47. description of the acon bits, Table 48. adc clock input – ST & T UPSD3212C User Manual

Page 66: Table

uPSD3212A, uPSD3212C, uPSD3212CV

66/163

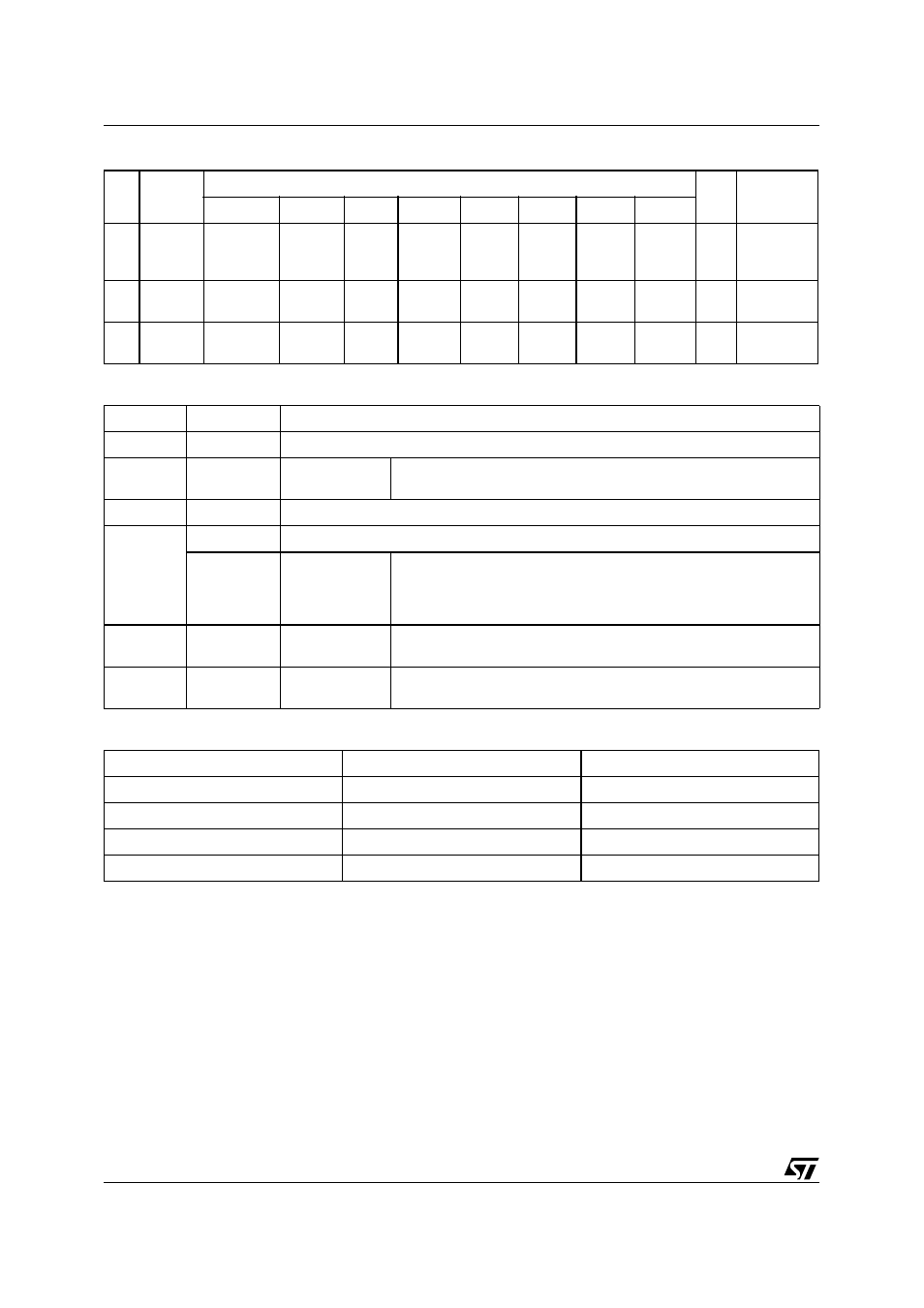

Table 46. ADC SFR Memory Map

Table 47. Description of the ACON Bits

Table 48. ADC Clock Input

SFR

Addr

Reg

Name

Bit Register Name

Reset

Value

Comments

7

6

5

4

3

2

1

0

95

ASCL

00

8-bit

Prescaler for

ADC clock

96

ADAT

ADAT7

ADAT6

ADAT5

ADAT4

ADAT3

ADAT2

ADAT1

ADAT0

00

ADC Data

Register

97

ACON

ADEN

ADS1

ADS0

ADST

ADSF

00

ADC Control

Register

Bit

Symbol

Function

7 to 6

—

Reserved

5

ADEN

ADC Enable Bit: 0 : ADC shut off and consumes no operating current

1 : enable ADC

4

—

Reserved

3 to 2

ADS1, ADS0

Analog channel select

0, 0

0, 1

1, 0

1, 1

Channel0 (ACH0)

Channel1 (ACH1)

Channel2 (ACH2)

Channel3 (ACH3)

1

ADST

ADC Start Bit:

0 : force to zero

1 : start an ADC; after one cycle, bit is cleared to '0'

0

ADSF

ADC Status Bit:

0 : A/D conversion is in process

1 : A/D conversion is completed, not in process

MCU Clock Frequency

Prescaler Register Value

ADC Clock

40MHz

2

6.7MHz

36MHz

2

6MHz

24MHz

1

6MHz

12MHz

0

6MHz