Table 122. a/d analog specification – ST & T UPSD3212C User Manual

Page 144

uPSD3212A, uPSD3212C, uPSD3212CV

144/163

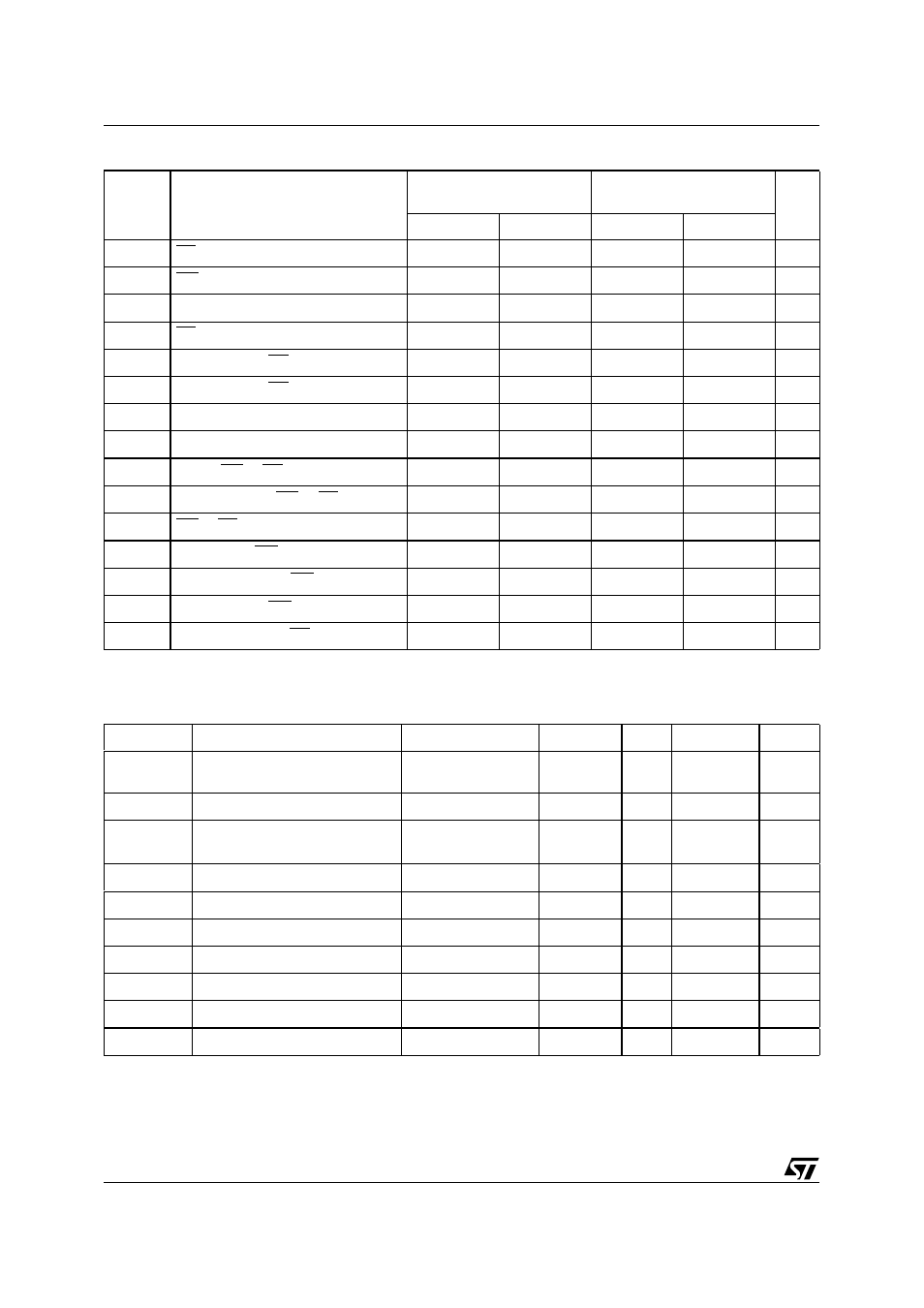

Table 121. External Data Memory AC Characteristics (with the 3V MCU Module)

Note: 1. Conditions (in addition to those in

, V

CC

= 3.0 to 3.6V): V

SS

= 0V; C

L

for Port 0, ALE and PSEN output is 100pF,

for 5V devices, and 50pF for 3V devices; C

L

for other outputs is 80pF, for 5V devices, and 50pF for 3V devices)

Table 122. A/D Analog Specification

Symbol

Parameter

(1)

24MHz Oscillator

Variable Oscillator

1/t

CLCL

= 8 to 24MHz

Unit

Min

Max

Min

Max

t

RLRH

RD pulse width

180

6t

CLCL

– 70

ns

t

WLWH

WR pulse width

180

6t

CLCL

– 70

ns

t

LLAX2

Address hold after ALE

56

2t

CLCL

– 27

ns

t

RHDX

RD to valid data in

118

5t

CLCL

– 90

ns

t

RHDX

Data hold after RD

0

0

ns

t

RHDZ

Data float after RD

63

2t

CLCL

– 20

ns

t

LLDV

ALE to valid data in

200

8t

CLCL

– 133

ns

t

AVDV

Address to valid data in

220

9t

CLCL

– 155

ns

t

LLWL

ALE to WR or RD

75

175

3t

CLCL

– 50

t

CLCL

+ 50

ns

t

AVWL

Address valid to WR or RD

67

4t

CLCL

– 97

ns

t

WHLH

WR or RD High to ALE High

17

67

t

CLCL

– 25

t

CLCL

+ 25

ns

t

QVWX

Data valid to WR transition

5

t

CLCL

– 37

ns

t

QVWH

Data set up before WR

170

7t

CLCL

– 122

ns

t

WHQX

Data hold after WR

15

t

CLCL

– 27

ns

t

RLAZ

Address float after RD

0

0

ns

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

AV

REF

Analog Power Supply Input

Voltage Range

V

SS

V

CC

V

V

AN

Analog Input Voltage Range

V

SS

– 0.3

AV

REF

+ 0.3

V

I

AVDD

Current Following between V

CC

and V

SS

200

µA

CA

IN

Overall Accuracy

±2

l.s.b.

N

NLE

Non-Linearity Error

±2

l.s.b.

N

DNLE

Differential Non-Linearity Error

±2

l.s.b.

N

ZOE

Zero-Offset Error

±2

l.s.b.

N

FSE

Full Scale Error

±2

l.s.b.

N

GE

Gain Error

±2

l.s.b.

T

CONV

Conversion Time

at 8MHz clock

20

µs