Pin package i/o port – ST & T UPSD3212C User Manual

Page 12

uPSD3212A, uPSD3212C, uPSD3212CV

12/163

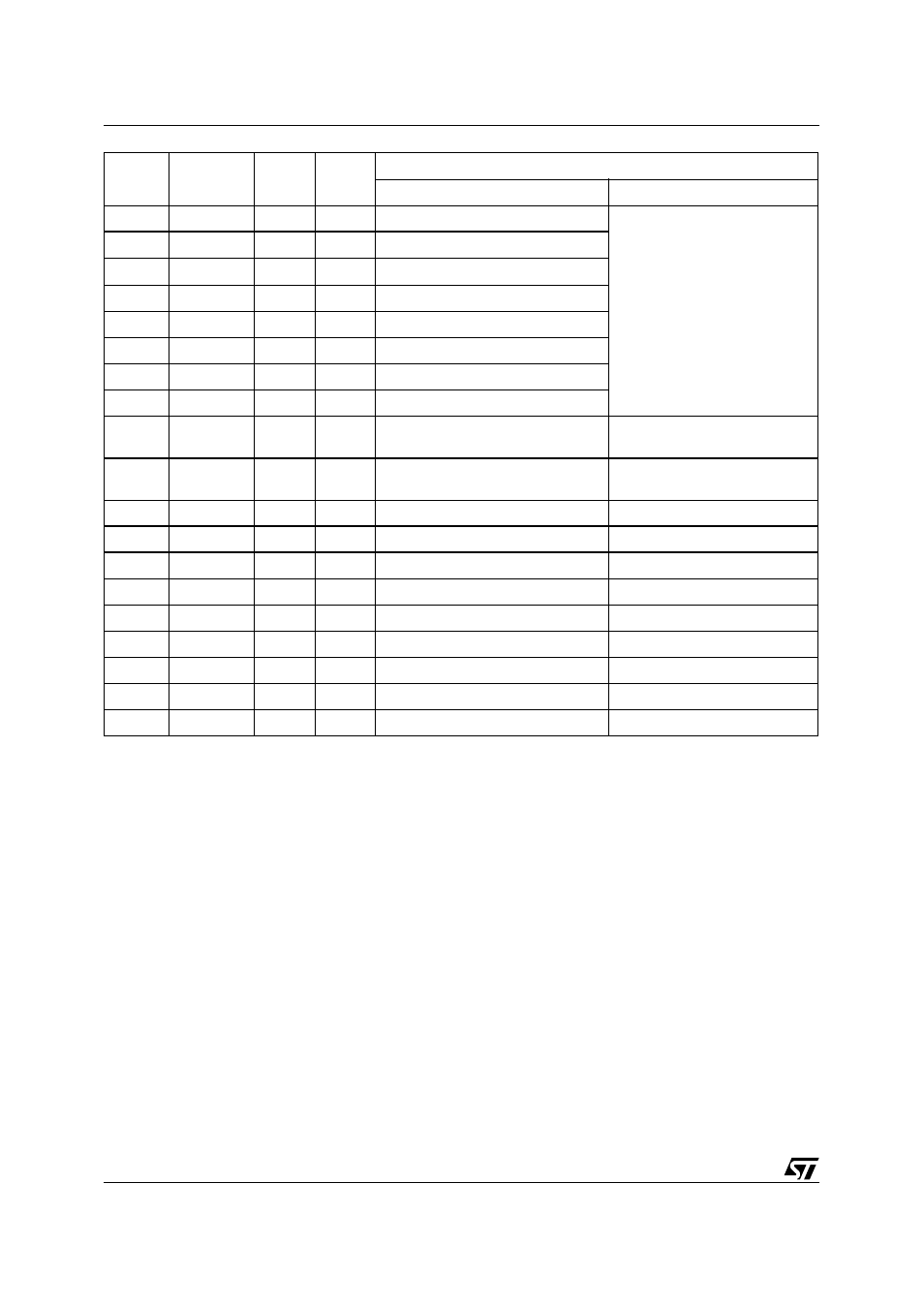

52-PIN PACKAGE I/O PORT

The 52-pin package members of the uPSD321x

Devices have the same port pins as those of the

80-pin package except:

–

Port 0 (P0.0-P0.7, external address/data bus

AD0-AD7)

–

Port 2 (P2.0-P2.3, external address bus A8-

A11)

–

Port A (PA0-PA7)

–

Port D (PD2)

–

Bus control signal (RD,WR,PSEN,ALE)

Pin 5 requires a pull-up resistor (2k

Ω

for 3V

devices, 7.5k

Ω

for 5V devices) for all devices.

JTAG TMS

20

I

JTAG pin

1.

PLD Macro-cell outputs

2.

PLD inputs

3.

SRAM stand by voltage in-

put (V

STBY

)

4.

SRAM battery-on indicator

(PC4)

5.

JTAG pins are dedicated

pins

JTAG TCK

16

I

JTAG pin

PC2

V

STBY

15

I/O

General I/O port pin

PC3

TSTAT

14

I/O

General I/O port pin

PC4

TERR_

9

I/O

General I/O port pin

JTAG TDI

7

I

JTAG pin

JTAG TDO

6

O

JTAG pin

PC7

5

I/O

General I/O port pin

PD1

CLKIN

3

I/O

General I/O port pin

1.

PLD I/O

2.

Clock input to PLD and APD

PD2

1

I/O

General I/O port pin

1.

PLD I/O

2.

Chip select to PSD Module

Vcc

12

Vcc

50

GND

13

GND

29

GND

69

USB+

10

NC

11

NC

17

NC

71

Port Pin

Signal

Name

Pin No.

In/Out

Function

Basic

Alternate