Figure 21. reset pulse width, Table 35. description of the wdrst bits – ST & T UPSD3212C User Manual

Page 47

47/163

uPSD3212A, uPSD3212C, uPSD3212CV

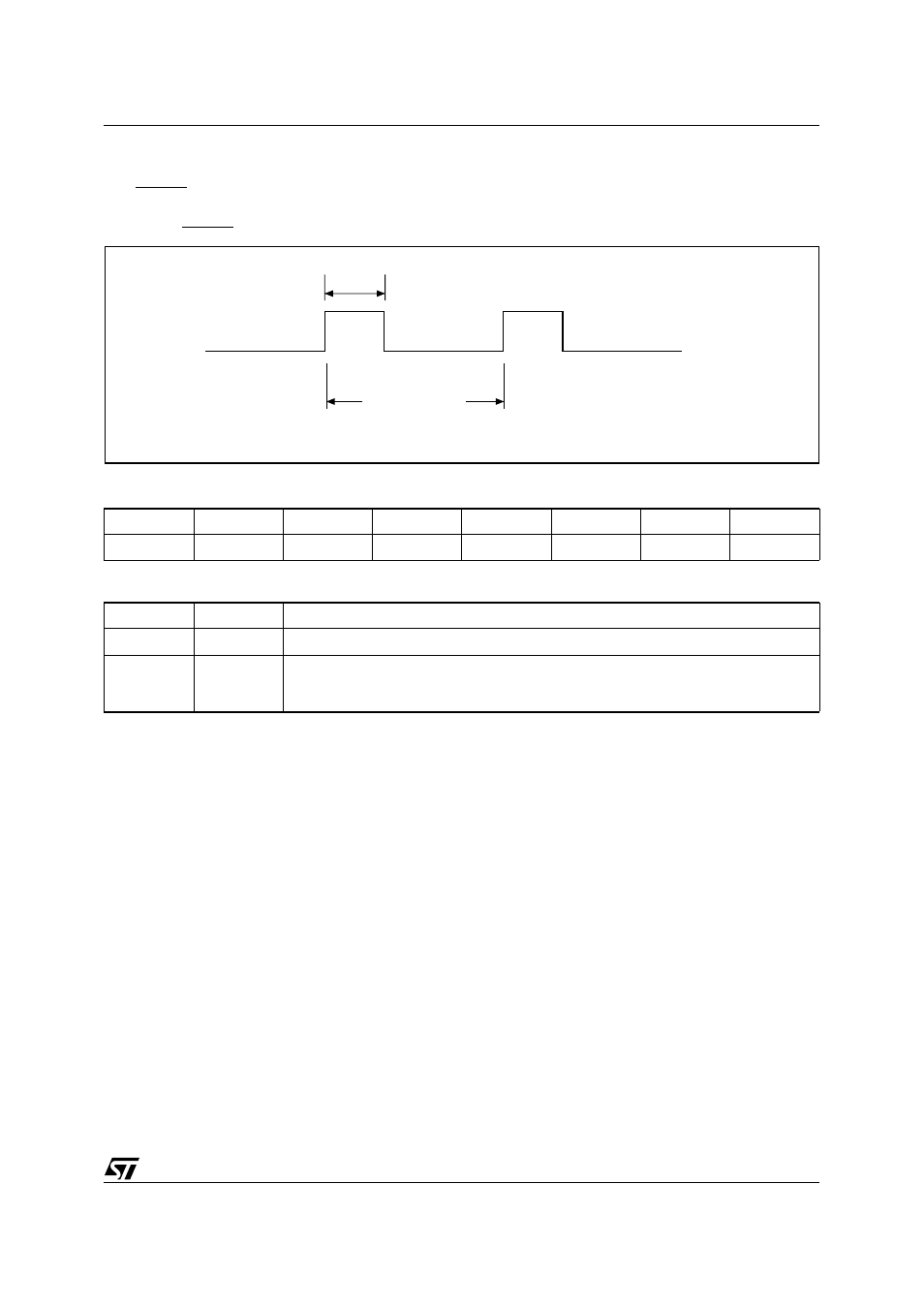

Watchdog reset pulse width depends on the clock

frequency. The reset period is Tf

OSC

x 12 x 2

22

.

The RESET pulse width is Tf

OSC

x 12 x 2

15

.

Figure 21. RESET Pulse Width

Table 34. Watchdog Timer Clear Register (WDRST: 0A6H)

Table 35. Description of the WDRST Bits

Note: The Watchdog Timer (WDT) is enabled at power-up or reset and must be served or disabled.

7

6

5

4

3

2

1

0

Reserved

WDRST6

WDRST5

WDRST4

WDRST3

WDRST2

WDRST1

WDRST0

Bit

Symbol

Function

7

—

Reserved

6 to 0

WDRST6 to

WDRST0

To reset Watchdog Timer, write any value beteen 00h and 7Eh to this register.

This value is loaded to the 7 most significant bits of the 22-bit counter.

For example: MOV WDRST,#1EH

Reset period

(1.258 second at 40Mhz)

(about 6.291 seconds at 8Mhz)

Reset pulse width (about 10ms at 40Mhz, about 50ms at 8Mhz)

AI06823