Figure 66. enable power-down flow chart, Table 98. power-down mode’s effect on ports – ST & T UPSD3212C User Manual

Page 123

123/163

uPSD3212A, uPSD3212C, uPSD3212CV

The PSD MODULE has a Turbo Bit in PMMR0.

This bit can be set to turn the Turbo Mode off (the

default is with Turbo Mode turned on). While Turbo

Mode is off, the PLDs can achieve standby current

when no PLD inputs are changing (zero DC cur-

rent). Even when inputs do change, significant

power can be saved at lower frequencies (AC cur-

rent), compared to when Turbo Mode is on. When

the Turbo Mode is on, there is a significant DC cur-

rent component and the AC component is higher.

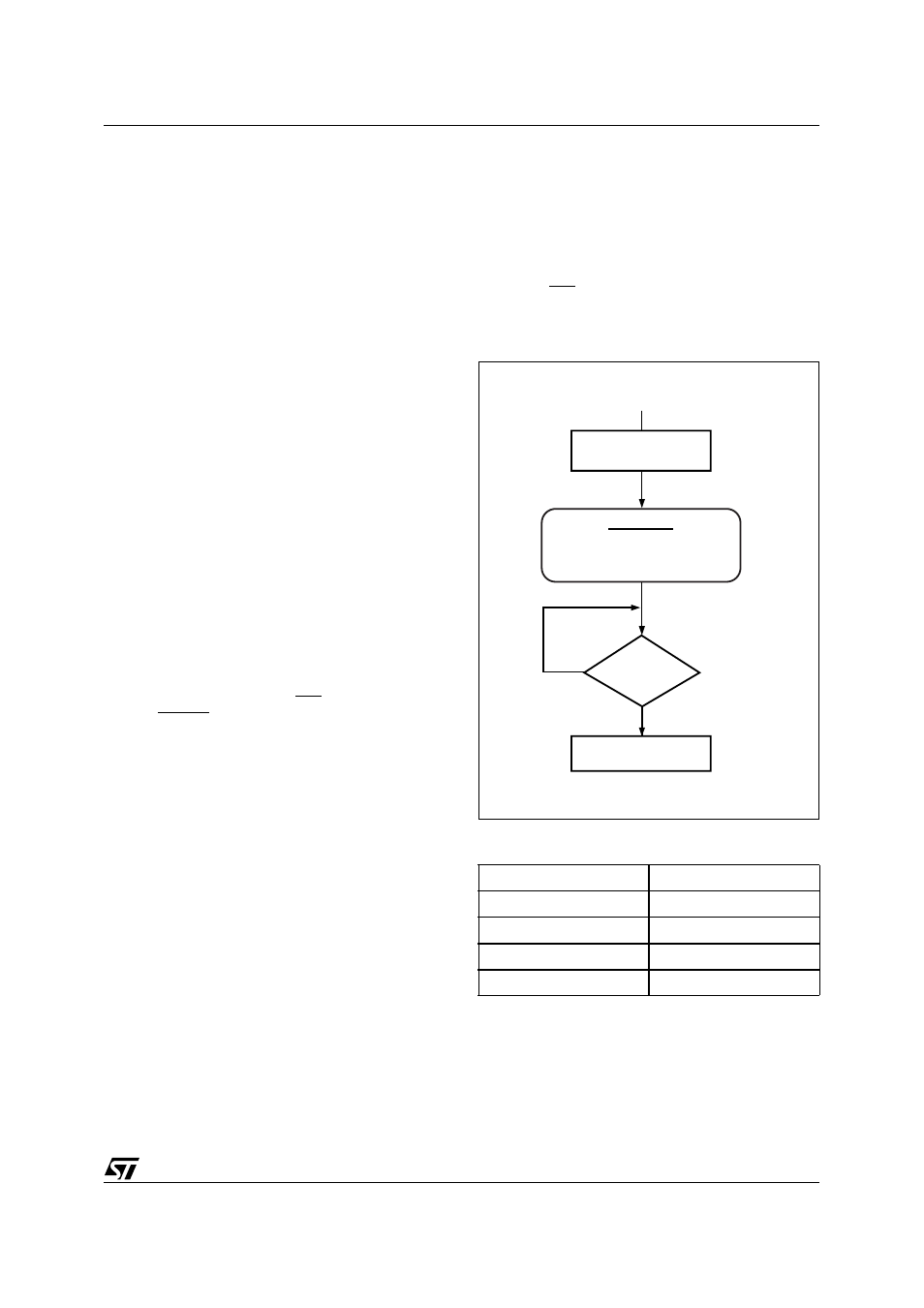

Automatic Power-down (APD) Unit and Power-

down Mode. The APD Unit, shown in

, puts the PSD MODULE into Pow-

er-down Mode by monitoring the activity of Ad-

dress Strobe (ALE). If the APD Unit is enabled, as

soon as activity on Address Strobe (ALE) stops, a

four-bit counter starts counting. If Address Strobe

(ALE/AS, PD0) remains inactive for fifteen clock

periods of CLKIN (PD1), Power-down (PDN) goes

High, and the PSD MODULE enters Power-down

Mode, as discussed next.

Power-down Mode. By default, if you enable the

APD Unit, Power-down Mode is automatically en-

abled. The device enters Power-down Mode if Ad-

dress Strobe (ALE) remains inactive for fifteen

periods of CLKIN (PD1).

The following should be kept in mind when the

PSD MODULE is in Power-down Mode:

–

If Address Strobe (ALE) starts pulsing again,

the PSD MODULE returns to normal

Operating mode. The PSD MODULE also

returns to normal Operating mode if either

PSD Chip Select Input (CSI, PD2) is Low or

the RESET input is High.

–

The MCU address/data bus is blocked from all

memory and PLDs.

–

Various signals can be blocked (prior to

Power-down Mode) from entering the PLDs by

setting the appropriate bits in the PMMR

registers. The blocked signals include MCU

control signals and the common CLKIN (PD1).

Note: Blocking CLKIN (PD1) from the PLDs

does not block CLKIN (PD1) from the APD

Unit.

–

All memories enter Standby Mode and are

drawing standby current. However, the PLD

and I/O ports blocks do

not

go into Standby

Mode because you don’t want to have to wait

for the logic and I/O to “wake-up” before their

outputs can change. See Table

for Power-

down Mode effects on PSD MODULE ports.

–

Typical standby current is of the order of

microamperes. These standby current values

assume that there are no transitions on any

PLD input.

Other Power Saving Options. The PSD MOD-

ULE offers other reduced power saving options

that are independent of the Power-down Mode.

Except for the SRAM Standby and PSD Chip Se-

lect Input (CSI, PD2) features, they are enabled by

setting bits in PMMR0 and PMMR2.

Figure 66. Enable Power-down Flow Chart

Table 98. Power-down Mode’s Effect on Ports

Port Function

Pin Level

MCU I/O

No Change

PLD Out

No Change

Address Out

Undefined

Peripheral I/O

Tri-State

Enable APD

Set PMMR0 Bit 1 = 1

PSD Module in Power

Down Mode

ALE idle

for 15 CLKIN

clocks?

RESET

Yes

No

OPTIONAL

Disable desired inputs to PLD

by setting PMMR0 bits 4 and 5

and PMMR2 bits 2 through 6.

AI06609