Table 51. description of the s2con bits – ST & T UPSD3212C User Manual

Page 73

73/163

uPSD3212A, uPSD3212C, uPSD3212CV

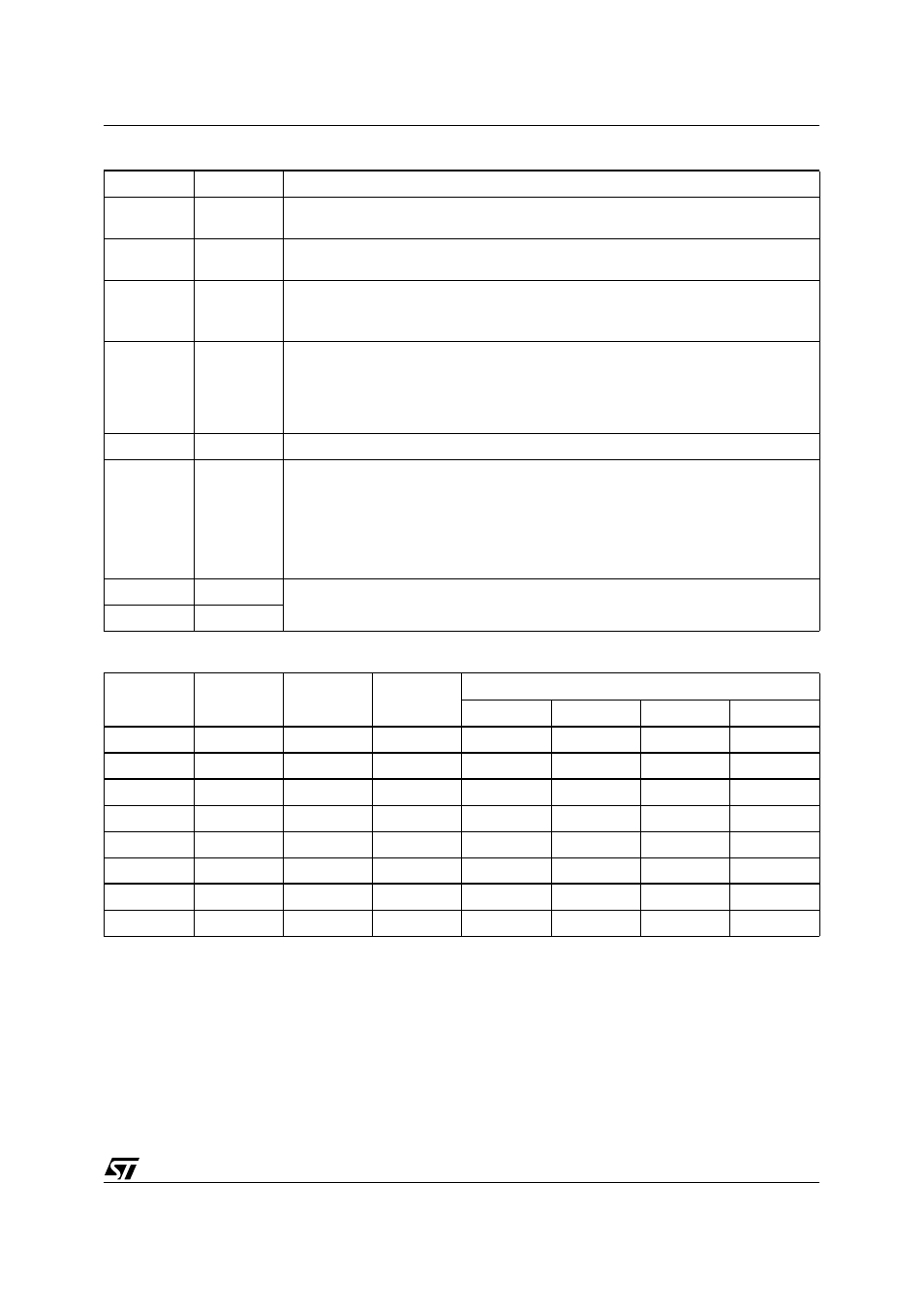

Table 51. Description of the S2CON Bits

Table 52. Selection of the Serial Clock Frequency SCL in Master Mode

Bit Symbol

Function

7

CR2

This bit along with Bits CR1and CR0 determines the serial clock frequency when SIO is

in the Master Mode.

6

ENII

Enable IIC. When ENI1 = 0, the IIC is disabled. SDA and SCL outputs are in the high

impedance state.

5

STA

START Flag. When this bit is set, the SIO H/W checks the status of the I

2

C-bus and

generates a START condition if the bus free. If the bus is busy, the SIO will generate a

repeated START condition when this bit is set.

4

STO

STOP Flag. With this bit set while in Master Mode a STOP condition is generated.

When a STOP condition is detected on the I

2

C bus, the I

2

C hardware clears the STO

Flag.

Note: This bit have to be set before 1 cycle interrupt period of STOP. That is, if this bit is

set, STOP condition in Master Mode is generated after 1 cycle interrupt period.

3

ADDR

This bit is set when address byte was received. Must be cleared by software.

2

AA

Acknowledge enable signal. If this bit is set, an acknowledge (low level to SDA) is

returned during the acknowledge clock pulse on the SCL line when:

• Own slave address is received

• A data byte is received while the device is programmed to be a Master Receiver

• A data byte is received while the device is a selected Slave Receiver. When this bit is

reset, no acknowledge is returned.

SIO release SDA line as high during the acknowledge clock pulse.

1

CR1

These two bits along with the CR2 Bit determine the serial clock frequency when SIO is

in the Master Mode.

0

CR0

CR2 CR1

CR0

f

OSC

Divisor

Bit Rate (kHz) at f

OSC

12MHz

24MHz

36MHz

40MHz

0

0

0

16

375

750

X

X

0

0

1

24

250

500

750

833

0

1

0

30

200

400

600

666

0

1

1

60

100

200

300

333

1

0

0

120

50

100

150

166

1

0

1

240

25

50

75

83

1

1

0

480

12.5

25

37.5

41

1

1

1

960

6.25

12.5

18.75

20