Usart interrupt, Interrupt priority structure, Interrupts enable structure – ST & T UPSD3212C User Manual

Page 36: Table 18. priority levels, Table 19. sfr register

uPSD3212A, uPSD3212C, uPSD3212CV

36/163

USART Interrupt

–

The USART Interrupt is generated by RI

(Receive Interrupt) OR TI (Transmit Interrupt).

–

When the USART Interrupt is generated, the

corresponding request flag must be cleared by

the software. The interrupt service routine will

have to check the various USART registers to

determine the source and clear the

corresponding flag.

–

Both USART’s are identical, except for the

additional interrupt controls in the Bit 4 of the

additional interrupt control registers (A7H,

B7H).

Interrupt Priority Structure

Each interrupt source can be assigned one of two

priority levels. Interrupt priority levels are defined

by the interrupt priority special function register IP

and IPA.

0 = low priority

1 = high priority

A low priority interrupt may be interrupted by a

high priority interrupt level interrupt. A high priority

interrupt routine cannot be interrupted by any oth-

er interrupt source. If two interrupts of different pri-

ority occur simultaneously, the high priority level

request is serviced. If requests of the same priority

are received simultaneously, an internal polling

sequence determines which request is serviced.

Thus, within each priority level, there is a second

priority structure determined by the polling se-

quence.

Interrupts Enable Structure

Each interrupt source can be individually enabled

or disabled by setting or clearing a bit in the inter-

rupt enable special function register IE and IEA. All

interrupt source can also be globally disabled by

the clearing Bit EA in IE (see Table

). Please

,

for individual bit de-

scriptions.

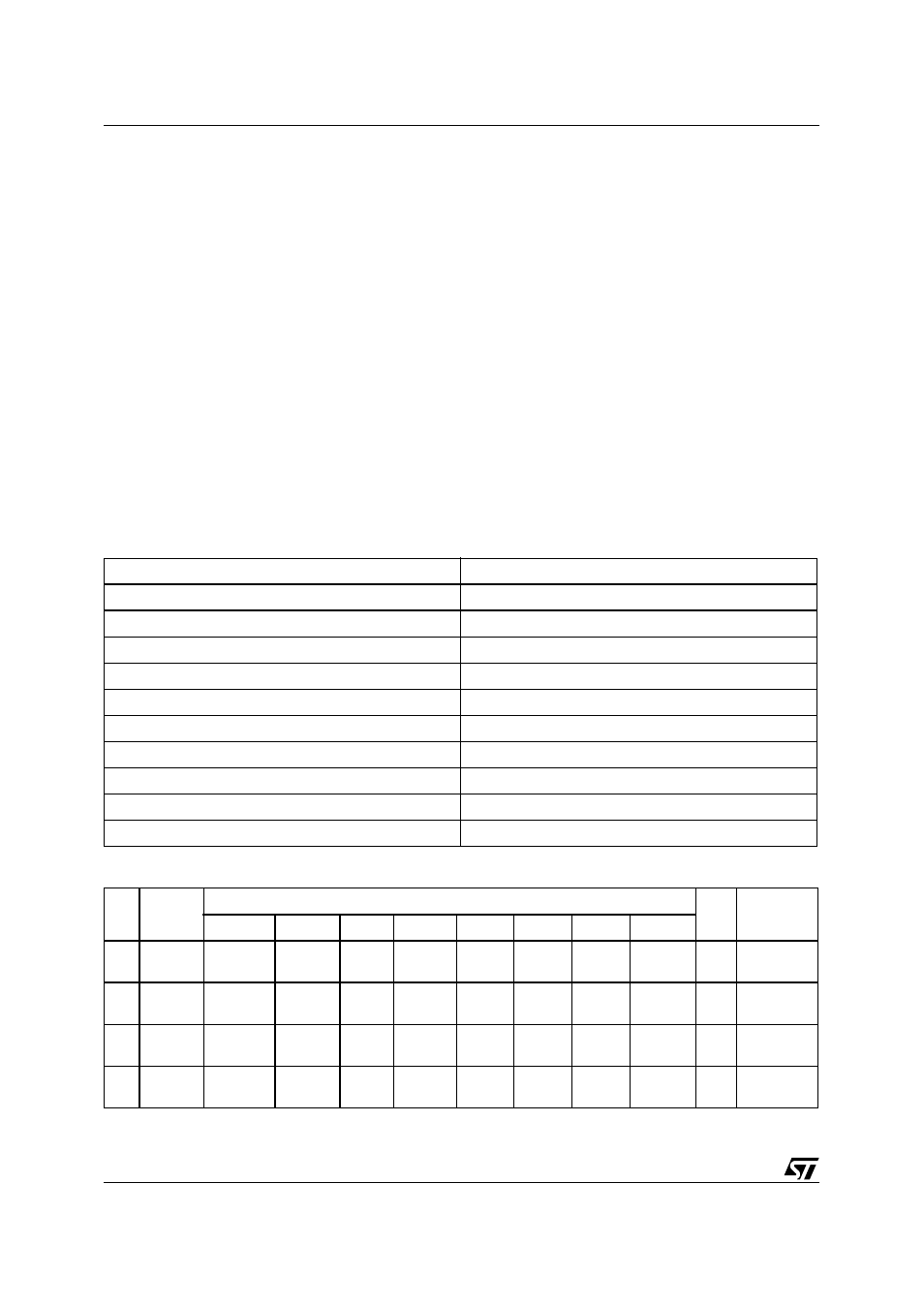

Table 18. Priority Levels

Table 19. SFR Register

Source

Priority with Level

Int0

0 (highest)

2nd USART

1

Timer 0

2

I²C

3

Int1

4

reserved

5

Timer 1

6

USB

7

1st USART

8

Timer 2+EXF2

9 (lowest)

SFR

Addr

Reg

Name

Bit Register Name

Reset

Value

Comments

7

6

5

4

3

2

1

0

A7

IEA

—

—

—

ES2

—

—

EI

2

C

EUSB

00

Interrupt

Enable (2nd)

A8

IE

EA

—

ET2

ES

ET1

EX1

ET0

EX0

00

Interrupt

Enable

B7

IPA

—

—

—

PS2

—

—

PI

2

C

PUSB

00

Interrupt

Priority (2nd)

B8

IP

—

—

PT2

PS

PT1

PX1

PT0

PX0

00

Interrupt

Priority