Sram, Sector select and sram select – ST & T UPSD3212C User Manual

Page 102

uPSD3212A, uPSD3212C, uPSD3212CV

102/163

SRAM

The SRAM is enabled when SRAM Select (RS0)

from the DPLD is High. SRAM Select (RS0) can

contain up to two product terms, allowing flexible

memory mapping.

The SRAM can be backed up using an external

battery. The external battery should be connected

to Voltage Standby (V

STBY

, PC2). If you have an

external battery connected to the uPSD3200, the

contents of the SRAM are retained in the event of

a power loss. The contents of the SRAM are re-

tained so long as the battery voltage remains at 2V

or greater. If the supply voltage falls below the bat-

tery voltage, an internal power switchover to the

battery occurs.

PC4 can be configured as an output that indicates

when power is being drawn from the external bat-

tery. Battery-on Indicator (V

BATON

, PC4) is High

with the supply voltage falls below the battery volt-

age and the battery on Voltage Standby (V

STBY

,

PC2) is supplying power to the internal SRAM.

SRAM Select (RS0), Voltage Standby (V

STBY

,

PC2) and Battery-on Indicator (V

BATON

, PC4) are

all configured using PSDsoft Express Configura-

tion.

Sector Select and SRAM Select

Sector Select (FS0-FS3, CSBOOT0-CSBOOT1)

and SRAM Select (RS0) are all outputs of the

DPLD. They are setup by writing equations for

them in PSDsoft Express. The following rules ap-

ply to the equations for these signals:

1.

Primary Flash memory and secondary Flash

memory Sector Select signals must

not

be

larger than the physical sector size.

2.

Any primary Flash memory sector must

not

be

mapped in the same memory space as

another Flash memory sector.

3.

A secondary Flash memory sector must

not

be

mapped in the same memory space as

another secondary Flash memory sector.

4.

SRAM, I/O, and Peripheral I/O spaces must

not

overlap.

5.

A secondary Flash memory sector

may

overlap a primary Flash memory sector. In

case of overlap, priority is given to the

secondary Flash memory sector.

6.

SRAM, I/O, and Peripheral I/O spaces

may

overlap any other memory sector. Priority is

given to the SRAM, I/O, or Peripheral I/O.

Example. FS0 is valid when the address is in the

range of 8000h to BFFFh, CSBOOT0 is valid from

8000h to 9FFFh, and RS0 is valid from 8000h to

87FFh. Any address in the range of RS0 always

accesses the SRAM. Any address in the range of

CSBOOT0 greater than 87FFh (and less than

9FFFh) automatically addresses secondary Flash

memory segment 0. Any address greater than

9FFFh accesses the primary Flash memory seg-

ment 0. You can see that half of the primary Flash

memory segment 0 and one-fourth of secondary

Flash memory segment 0 cannot be accessed in

this example.

Note: An equation that defined FS1 to anywhere

in the range of 8000h to BFFFh would

not

be valid.

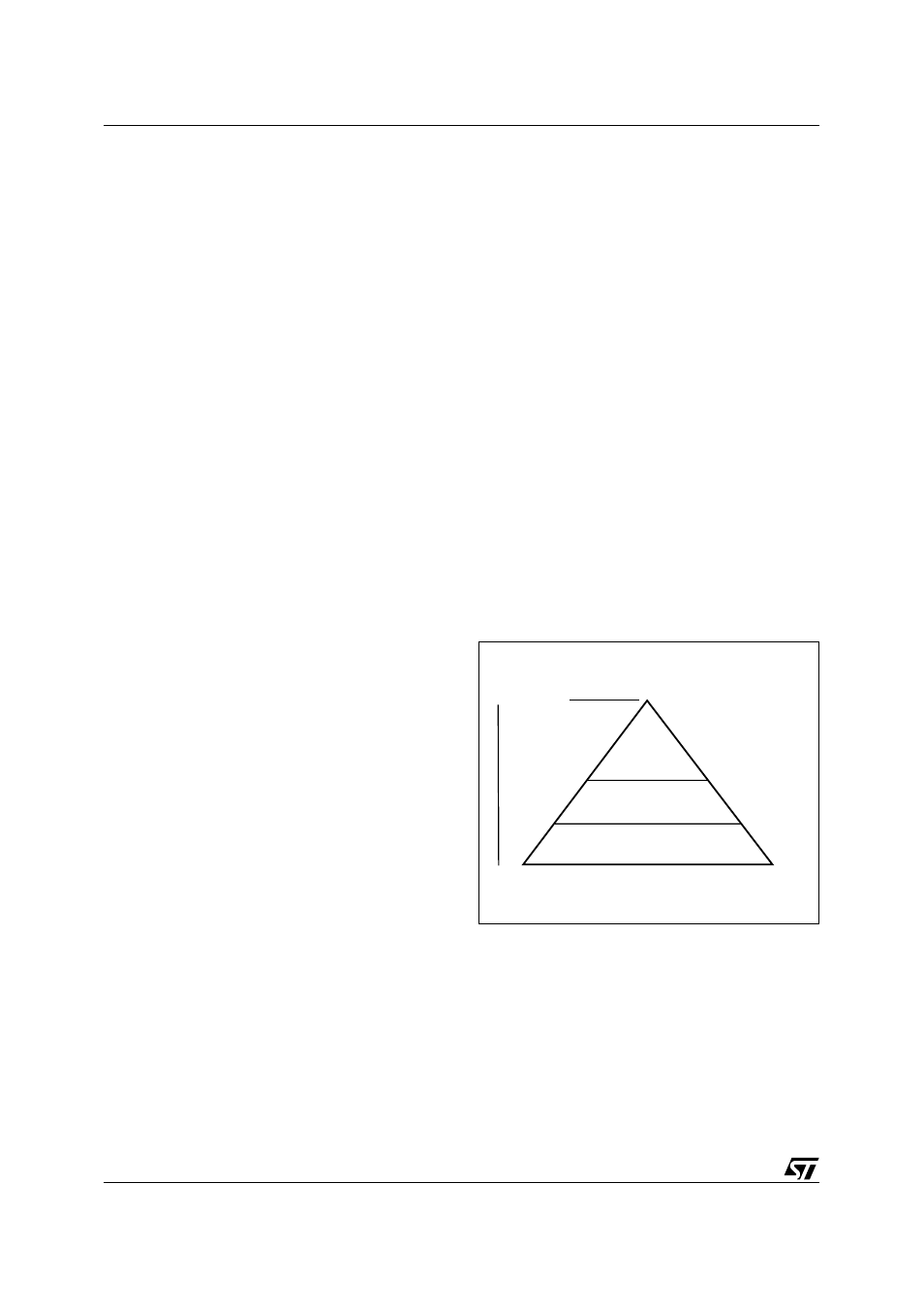

Figure

shows the priority levels for all memory

components. Any component on a higher level can

overlap and has priority over any component on a

lower level. Components on the same level must

not

overlap. Level one has the highest priority and

level 3 has the lowest.

Figure 50. Priority Level of Memory and I/O

Components in the PSD MODULE

Level 1

SRAM, I /O, or

Peripheral I /O

Level 2

Secondary

Non-Volatile Memory

Highest Priority

Lowest Priority

Level 3

Primary Flash Memory

AI02867D