Table 67. description of the ucon0 bits – ST & T UPSD3212C User Manual

Page 79

79/163

uPSD3212A, uPSD3212C, uPSD3212CV

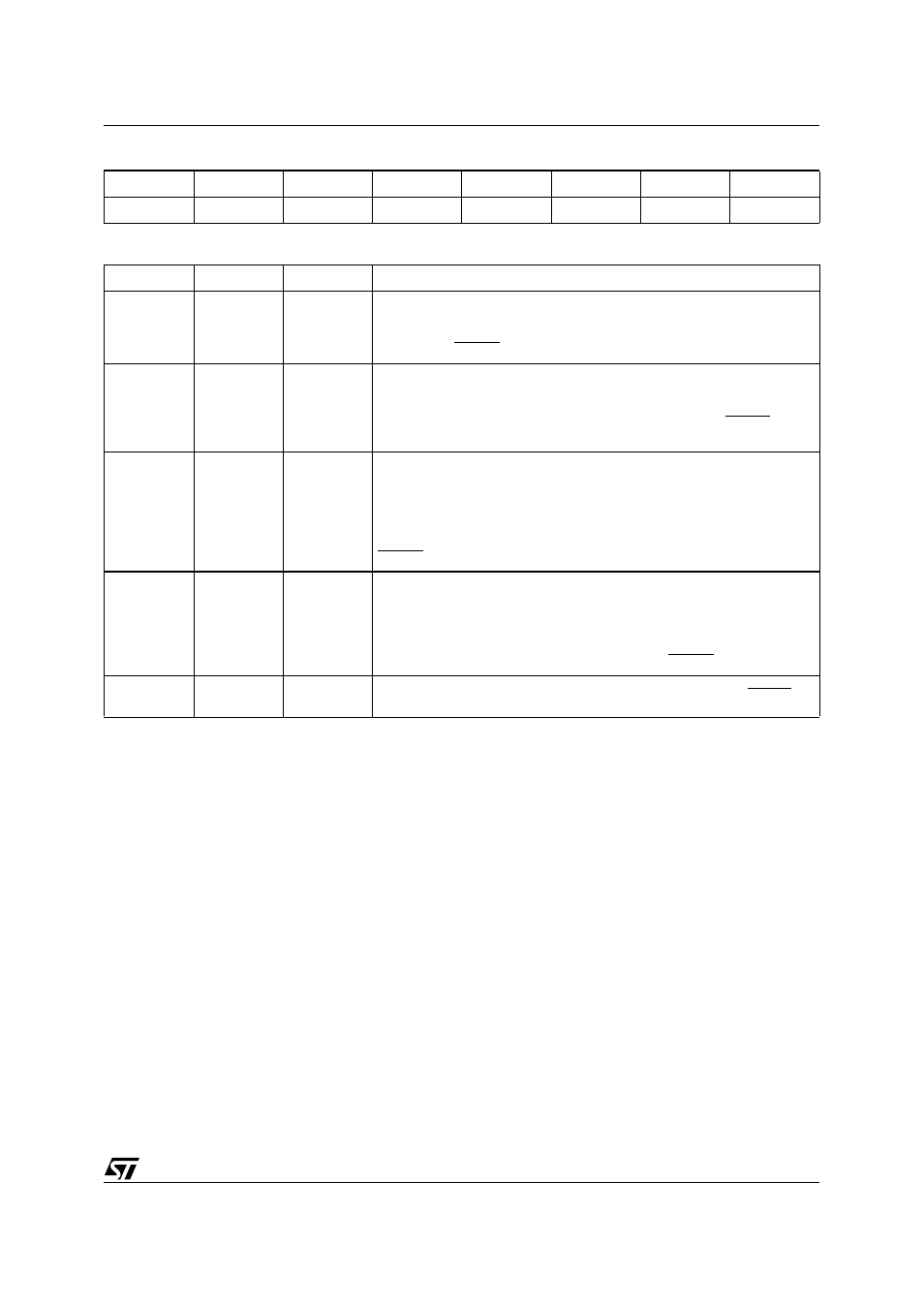

Table 66. USB Endpoint0 Transmit Control Register (UCON0: 0EAh)

Table 67. Description of the UCON0 Bits

7

6

5

4

3

2

1

0

TSEQ0

STALL0

TX0E

RX0E

TP0SIZ3

TP0SIZ2

TP0SIZ1

TP0SIZ0

Bit

Symbol

R/W

Function

7

TSEQ0

R/W

Endpoint0 Data Sequence Bit. (0=DATA0, 1=DATA1)

This bit determines which type of data packet (DATA0 or DATA1) will be

sent during the next IN transaction. Toggling of this bit must be controlled

by software. RESET clears this bit

6

STALL0

R/W

Endpoint0 Force Stall Bit.

This bit causes Endpoint 0 to return a STALL handshake when polled by

either an IN or OUT token by the USB Host Controller. The USB

hardware clears this bit when a SETUP token is received. RESET clears

this bit.

5

TX0E

R/W

Endpoint0 Transmit Enable.

This bit enables a transmit to occur when the USB Host Controller sends

an IN token to Endpoint 0. Software should set this bit when data is ready

to be transmitted. It must be cleared by software when no more Endpoint

0 data needs to be transmitted. If this bit is '0' or the TXD0F is set, the

USB will respond with a NAK handshake to any Endpoint 0 IN tokens.

RESET clears this bit.

4

RX0E

R/W

Endpoint0 receive enable.

This bit enables a receive to occur when the USB Host Controller sends

an OUT token to Endpoint 0. Software should set this bit when data is

ready to be received. It must be cleared by software when data cannot be

received. If this bit is '0' or the RXD0F is set, the USB will respond with a

NAK handshake to any Endpoint 0 OUT tokens. RESET clears this bit.

3 to 0

TP0SIZ3 to

TP0SIZ0

R/W

The number of transmit data bytes. These bits are cleared by RESET.