Pld power management, Psd chip select input (csi, pd2), Input clock – ST & T UPSD3212C User Manual

Page 124: Input control signals, Table 99. power management mode registers pmmr0

uPSD3212A, uPSD3212C, uPSD3212CV

124/163

PLD Power Management

The power and speed of the PLDs are controlled

by the Turbo Bit (Bit 3) in PMMR0 (see Table

By setting the bit to '1,' the Turbo Mode is off and

the PLDs consume the specified standby current

when the inputs are not switching for an extended

time of 70ns. The propagation delay time is in-

creased by 10ns (for a 5V device) after the Turbo

Bit is set to '1' (turned off) when the inputs change

at a composite frequency of less than 15MHz.

When the Turbo Bit is reset to '0' (turned on), the

PLDs run at full power and speed. The Turbo Bit

affects the PLD’s DC power, AC power, and prop-

agation delay. When the Turbo Mode is off, the

uPSD3200 input clock frequency is reduced by

5MHz from the maximum rated clock frequency.

Blocking MCU control signals with the bits of

PMMR2 (see

) can further

reduce PLD AC power consumption.

SRAM Standby Mode (Battery Backup). The

SRAM in the PSD MODULE supports a battery

backup mode in which the contents are retained in

the event of a power loss. The SRAM has Voltage

Standby (V

STBY

, PC2) that can be connected to an

external battery. When V

CC

becomes lower than

V

STBY

then the SRAM automatically connects to

Voltage Standby (V

STBY

, PC2) as a power source.

The SRAM Standby Current (I

STBY

) is typically 0.5

µA. The SRAM data retention voltage is 2V mini-

mum. The Battery-on Indicator (V

BATON

) can be

routed to PC4. This signal indicates when the V

CC

has dropped below V

STBY

.

PSD Chip Select Input (CSI, PD2)

PD2 of Port D can be configured in PSDsoft Ex-

press as PSD Chip Select Input (CSI). When Low,

the signal selects and enables the PSD MODULE

Flash memory, SRAM, and I/O blocks for READ or

WRITE operations. A High on PSD Chip Select In-

put (CSI, PD2) disables the Flash memory, and

SRAM, and reduces power consumption. Howev-

er, the PLD and I/O signals remain operational

when PSD Chip Select Input (CSI, PD2) is High.

Input Clock

CLKIN (PD1) can be turned off, to the PLD to save

AC power consumption. CLKIN (PD1) is an input

to the PLD AND Array and the Output Macrocells

(OMC).

During Power-down Mode, or, if CLKIN (PD1) is

not being used as part of the PLD logic equation,

the clock should be disabled to save AC power.

CLKIN (PD1) is disconnected from the PLD AND

Array or the Macrocells block by setting Bits 4 or 5

to a '1' in PMMR0.

Input Control Signals

The PSD MODULE provides the option to turn off

the MCU signals (WR, RD, PSEN, and Address

Strobe (ALE)) to the PLD to save AC power con-

sumption (see

). These con-

trol signals are inputs to the PLD AND Array.

During Power-down Mode, or, if any of them are

not being used as part of the PLD logic equation,

these control signals should be disabled to save

AC power. They are disconnected from the PLD

AND Array by setting Bits 2, 3, 4, 5, and 6 to a '1'

in PMMR2.

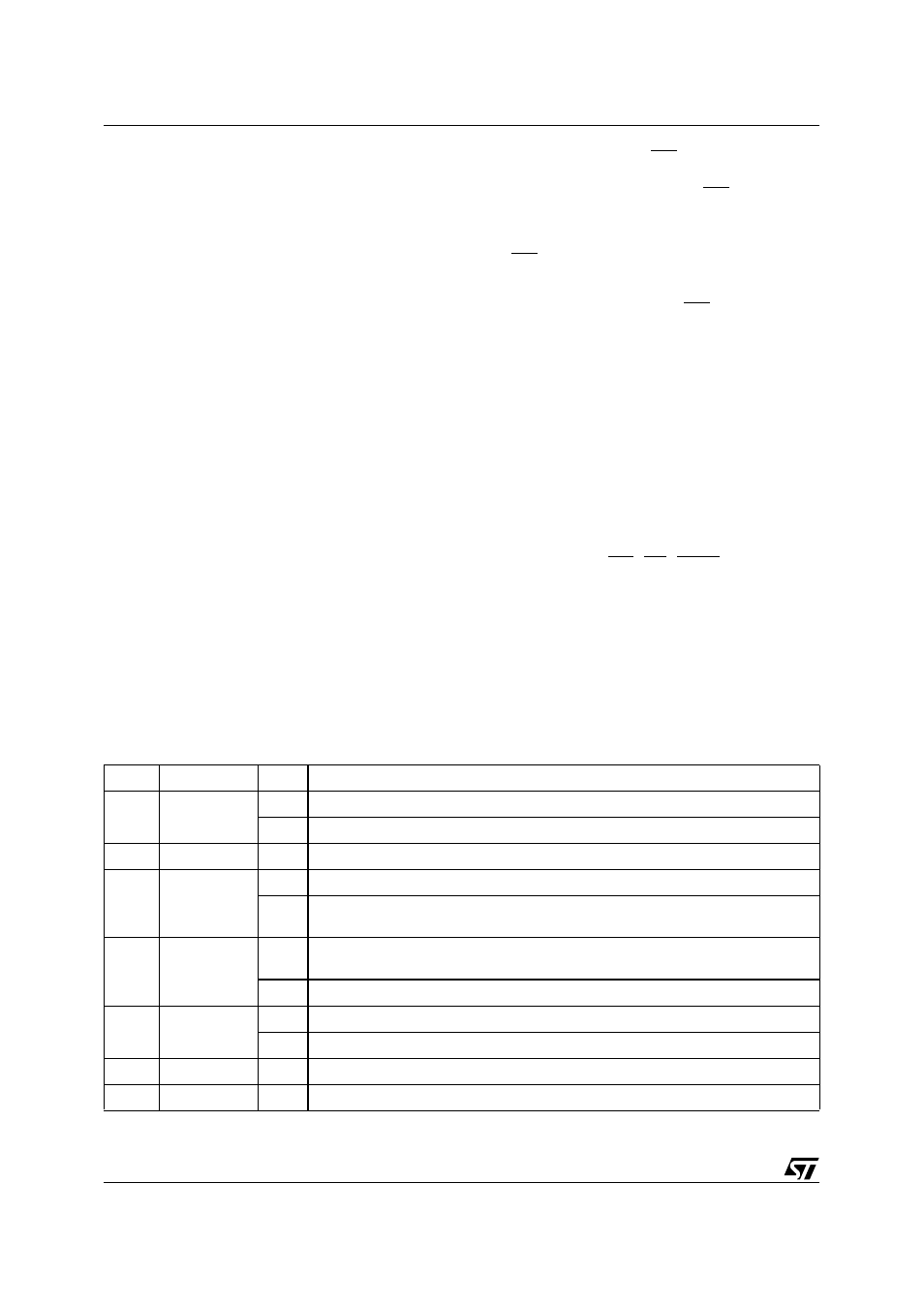

Table 99. Power Management Mode Registers PMMR0

Bit 0

X

0

Not used, and should be set to zero.

Bit 1

APD Enable

0 = off Automatic Power-down (APD) is disabled.

1 = on Automatic Power-down (APD) is enabled.

Bit 2

X

0

Not used, and should be set to zero.

Bit 3

PLD Turbo

0 = on PLD Turbo Mode is on

1 = off

PLD Turbo Mode is off, saving power.

uPSD3200 operates at 5MHz below the maximum rated clock frequency

Bit 4

PLD Array clk

0 = on

CLKIN (PD1) input to the PLD AND Array is connected. Every change of CLKIN

(PD1) Powers-up the PLD when Turbo Bit is '0.'

1 = off CLKIN (PD1) input to PLD AND Array is disconnected, saving power.

Bit 5

PLD MCell clk

0 = on CLKIN (PD1) input to the PLD macrocells is connected.

1 = off CLKIN (PD1) input to PLD macrocells is disconnected, saving power.

Bit 6

X

0

Not used, and should be set to zero.

Bit 7

X

0

Not used, and should be set to zero.