Power-saving mode, Idle mode, Power-down mode – ST & T UPSD3212C User Manual

Page 39: Power control register, Table 25. power-saving mode power consumption

39/163

uPSD3212A, uPSD3212C, uPSD3212CV

POWER-SAVING MODE

Two software selectable modes of reduced power

consumption are implemented (see Table

Idle Mode

The following Functions are Switched Off.

–

CPU (Halted)

The following Function Remain Active During Idle

Mode.

–

External Interrupts

–

Timer 0, Timer 1, Timer 2

–

PWM Units

–

USART

–

8-bit ADC

–

I

2

C Interface

–

USB Interface

Note: Interrupt or RESET terminates the Idle

Mode.

Power-Down Mode

–

System Clock Halted

–

LVD Logic Remains Active

–

SRAM contents remains unchanged

–

The SFRs retain their value until a RESET is

asserted

Note: The only way to exit Power-down Mode is a

RESET.

Power Control Register

The Idle and Power-down Modes are activated by

software via the PCON register (see Tables

and

Idle Mode

The instruction that sets PCON.0 is the last in-

struction executed in the normal operating mode

before Idle Mode is activated. Once in the Idle

Mode, the CPU status is preserved in its entirety:

Stack pointer, Program counter, Program status

word, Accumulator, RAM and All other registers

maintain their data during Idle Mode.

There are three ways to terminate the Idle Mode.

–

Activation of any enabled interrupt will cause

PCON.0 to be cleared by hardware

terminating Idle mode. The interrupt is

serviced, and following return from interrupt

instruction RETI, the next instruction to be

executed will be the one which follows the

instruction that wrote a logic '1' to PCON.0.

–

External hardware reset: the hardware reset is

required to be active for two machine cycle to

complete the RESET operation.

–

Internal reset: the microcontroller restarts after

3 machine cycles in all cases.

Power-Down Mode

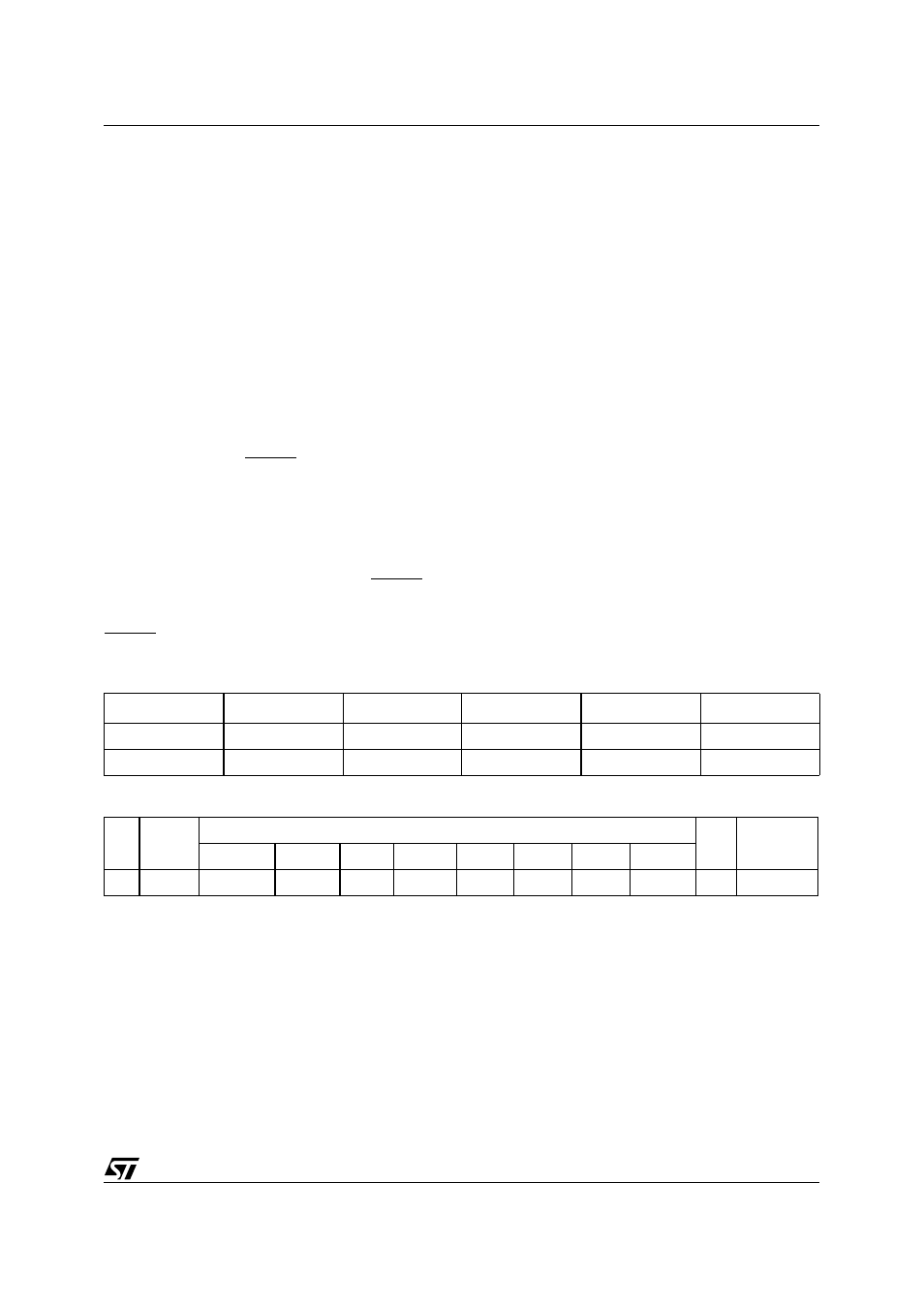

Table 25. Power-Saving Mode Power Consumption

Table 26. Pin Status During Idle and Power-down Mode

Mode

Addr/Data

Ports1,3,4

PWM

I

2

C

USB

Idle

Maintain Data

Maintain Data

Active

Active

Active

Power-down

Maintain Data

Maintain Data

Disable

Disable

Disable

SFR

Addr

Reg

Name

Bit Register Name

Reset

Value

Comments

7

6

5

4

3

2

1

0

87

PCON

SMOD

SMOD1

LVREN ADSFINT RCLK1

TCLK1

PD

IDLE

00

Power Ctrl