Table 23. description of the ipa bits, How interrupts are handled, Table 24. vector addresses – ST & T UPSD3212C User Manual

Page 38

uPSD3212A, uPSD3212C, uPSD3212CV

38/163

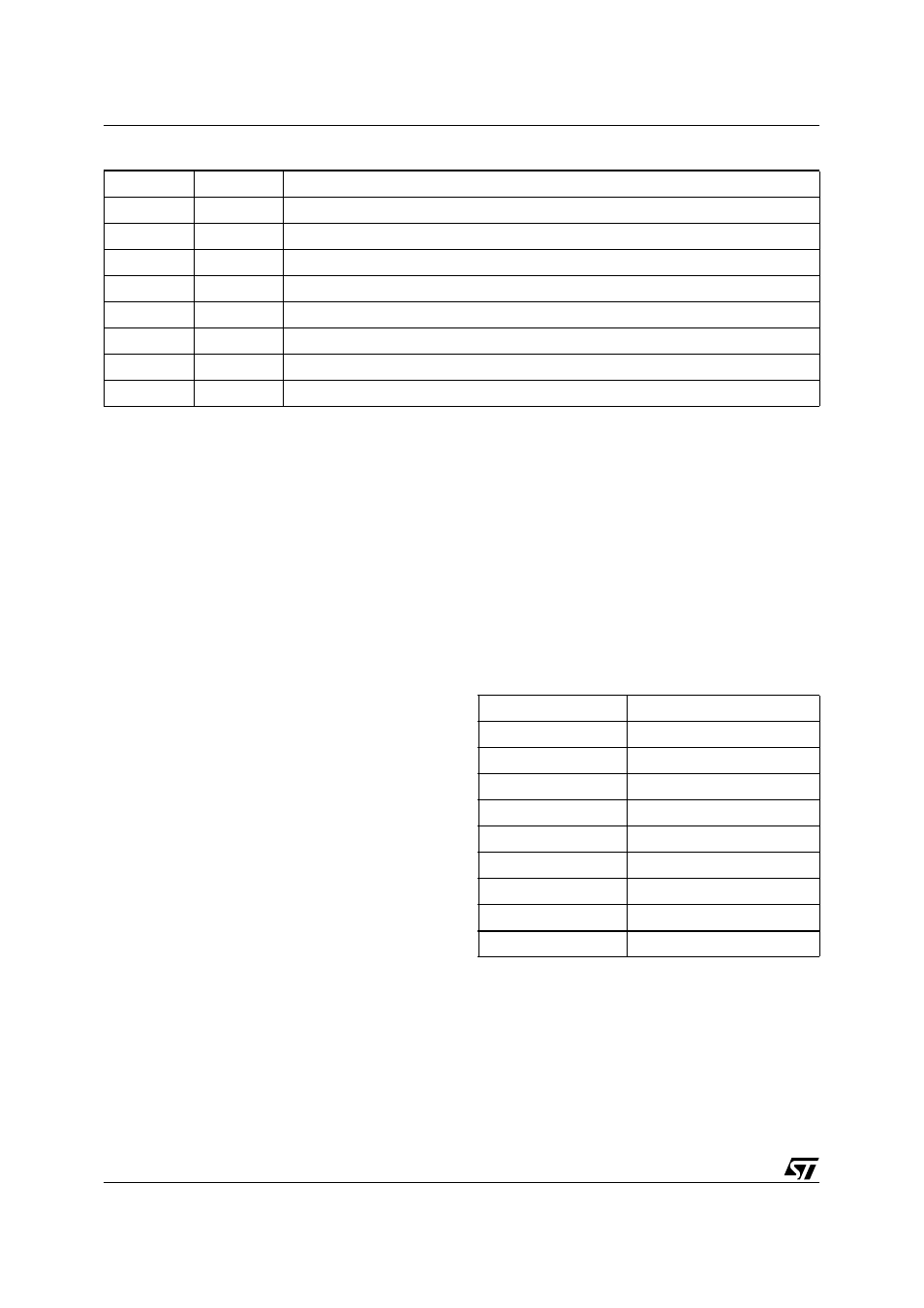

Table 23. Description of the IPA Bits

How Interrupts are Handled

The interrupt flags are sampled at S5P2 of every

machine cycle. The samples are polled during fol-

lowing machine cycle. If one of the flags was in a

set condition at S5P2 of the preceding cycle, the

polling cycle will find it and the interrupt system will

generate an LCALL to the appropriate service rou-

tine, provided this H/W generated LCALL is not

blocked by any of the following conditions:

–

An interrupt of equal priority or higher priority

level is already in progress.

–

The current machine cycle is not the final cycle

in the execution of the instruction in progress.

–

The instruction in progress is RETI or any

access to the interrupt priority or interrupt

enable registers.

The polling cycle is repeated with each machine

cycle, and the values polled are the values that

were present at S5P2 of the previous machine cy-

cle.

Note: If an interrupt flag is active but being re-

sponded to for one of the above mentioned condi-

tions, if the flag is still inactive when the blocking

condition is removed, the denied interrupt will not

be serviced. In other words, the fact that the inter-

rupt flag was once active but not serviced is not re-

membered. Every polling cycle is new.

The processor acknowledges an interrupt request

by executing a hardware generated LCALL to the

appropriate service routine. The hardware gener-

ated LCALL pushes the contents of the Program

Counter on to the stack (but it does not save the

PSW) and reloads the PC with an address that de-

pends on the source of the interrupt being vec-

tored to as shown in Table

.

Execution proceeds from that location until the

RETI instruction is encountered. The RETI instruc-

tion informs the processor that the interrupt routine

is no longer in progress, then pops the top two

bytes from the stack and reloads the Program

Counter. Execution of the interrupted program

continues from where it left off.

Note: A simple RET instruction would also return

execution to the interrupted program, but it would

have left the interrupt control system thinking an

interrupt was still in progress, making future inter-

rupts impossible.

Table 24. Vector Addresses

Bit

Symbol

Function

7

—

Not used

6

—

Not used

5

—

Not used

4

PS2

2nd USART Interrupt priority level

3

—

Not used

2

—

Not used

1

PI2C

I²C Interrupt priority level

0

PUSB

USB Interrupt priority level

Source

Vector Address

Int0

0003h

2nd USART

004Bh

Timer 0

000Bh

I²C

0043h

Int1

0013h

Timer 1

001Bh

USB

0033h

1st USART

0023h

Timer 2+EXF2

002Bh