ST & T UPSD3212C User Manual

Page 30

uPSD3212A, uPSD3212C, uPSD3212CV

30/163

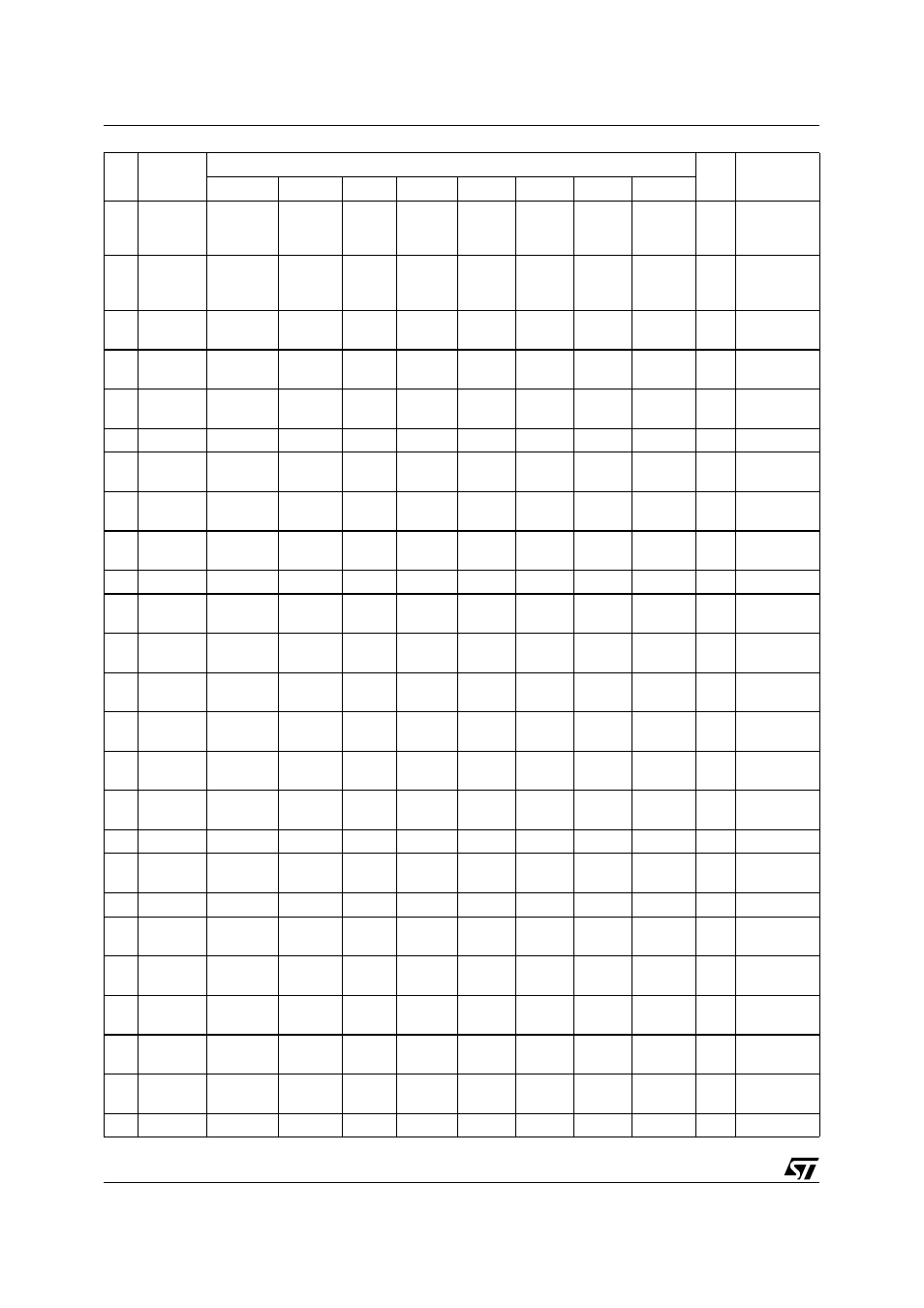

A4

PWM2

00

PWM2

Output Duty

Cycle

A5

PWM3

00

PWM3

Output Duty

Cycle

A6

WDRST

00

Watch Dog

Reset

A7

IEA

ES2

EI

2

C

00

Interrupt

Enable (2nd)

A8

IE

EA

-

ET2

ES

ET1

EX1

ET0

EX0

00

Interrupt

Enable

A9

AA

PWM4P

00

PWM 4

Period

AB

PWM4W

00

PWM 4 Pulse

Width

AE

WDKEY

00

Watch Dog

Key Register

B0

P3

FF

Port 3

B1

PSCL0L

00

Prescaler 0

Low (8-bit)

B2

PSCL0H

00

Prescaler 0

High (8-bit)

B3

PSCL1L

00

Prescaler 1

Low (8-bit)

B4

PSCL1H

00

Prescaler 1

High (8-bit)

B7

IPA

PS2

PI2C

00

Interrupt

Priority (2nd)

B8

IP

PT2

PS

PT1

PX1

PT0

PX0

00

Interrupt

Priority

C0

P4

FF

New Port 4

C8

T2CON

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/T2

CP/RL2

00

Timer 2

Control

C9

T2MOD

DCEN

00

Timer 2 Mode

CA

RCAP2L

00

Timer 2

Reload low

CB

RCAP2H

00

Timer 2

Reload High

CC

TL2

00

Timer 2 Low

byte

CD

TH2

00

Timer 2 High

byte

D0

PSW

CY

AC

FO

RS1

RS0

OV

P

00

Program

Status Word

D1

SFR

Addr

Reg Name

Bit Register Name

Reset

Value

Comments

7

6

5

4

3

2

1

0