Usb hardware, Usb related registers, Table 60. usb address register (uadr: 0eeh) – ST & T UPSD3212C User Manual

Page 76: Table 61. description of the uadr bits

uPSD3212A, uPSD3212C, uPSD3212CV

76/163

USB HARDWARE

The characteristics of USB hardware are as fol-

lows:

■

Complies with the Universal Serial Bus

specification Rev. 1.1

■

Integrated SIE (Serial Interface Engine), FIFO

memory and transceiver

■

Low speed (1.5Mbit/s) device capability

■

Supports control endpoint0 and interrupt

endpoint1 and 2

■

USB clock input must be 6MHz (requires MCU

clock frequency to be 12, 24, or 36MHz).

The analog front-end is an on-chip generic USB

transceiver. It is designed to allow voltage levels

equal to V

DD

from the standard logic to interface

with the physical layer of the Universal Serial Bus.

It is capable of receiving and transmitting serial

data at low speed (1.5Mb/s).

The SIE is the digital-front-end of the USB block.

This module recovers the 1.5MHz clock, detects

the USB sync word and handles all low-level USB

protocols and error checking. The bit-clock recov-

ery circuit recovers the clock from the incoming

USB data stream and is able to track jitter and fre-

quency drift according to the USB specification.

The SIE also translates the electrical USB signals

into bytes or signals. Depending upon the device

USB address and the USB endpoint.

Address, the USB data is directed to the correct

endpoint on SIE interface. The data transfer of this

H/W could be of type control or interrupt.

The device’s USB address and the enabling of the

endpoints are programmable in the SIE configura-

tion header.

USB related registers

The USB block is controlled via seven registers in

the memory: (UADR, UCON0, UCON1, UCON2,

UISTA, UIEN, and USTA).

Three memory locations on chip which communi-

cate the USB block are:

■

USB endpoint0 data transmit register (UDT0)

■

USB endpoint0 data receive register (UDR0)

■

USB endpoint1 data transmit register (UDT1)

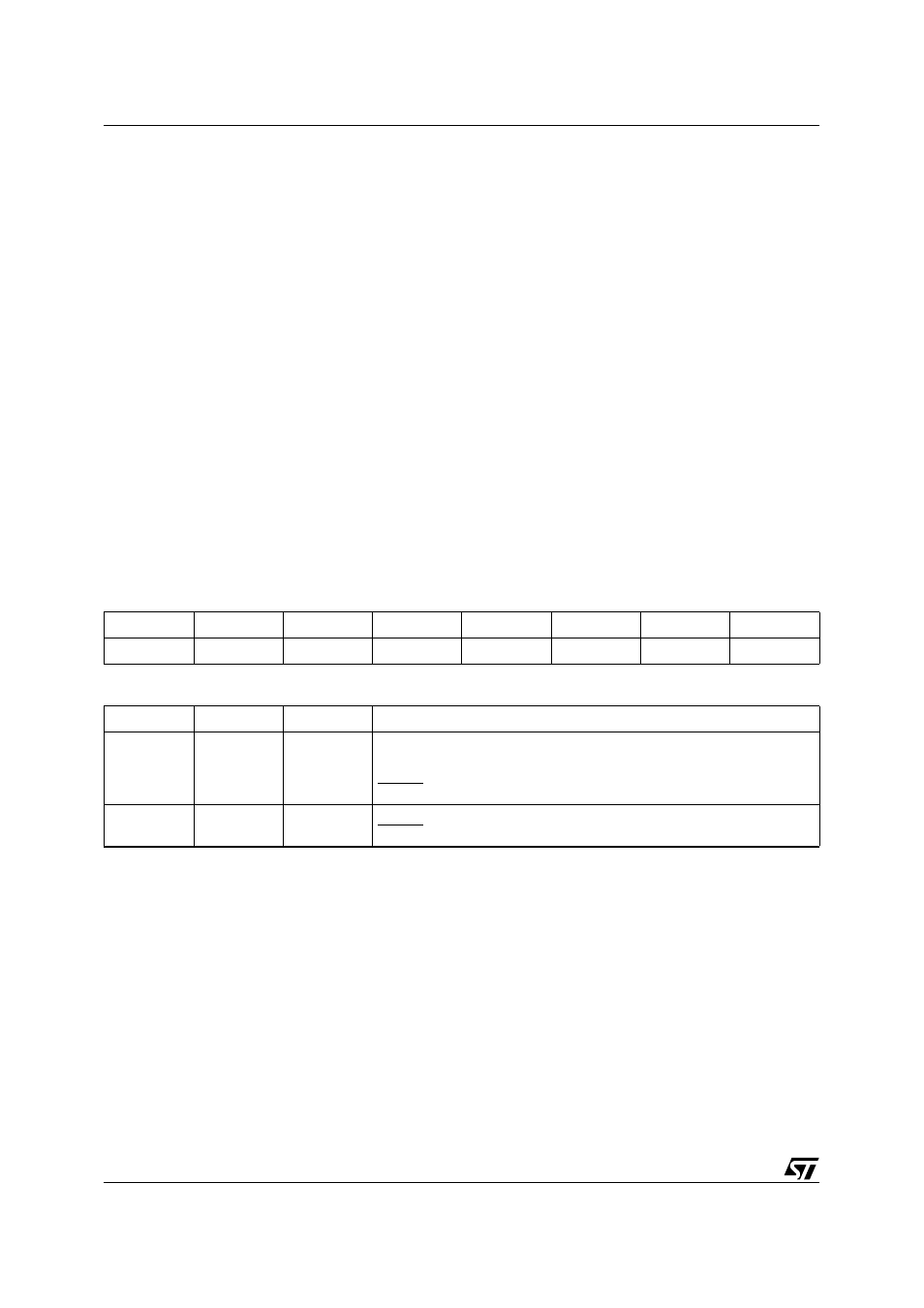

Table 60. USB Address Register (UADR: 0EEh)

Table 61. Description of the UADR Bits

7

6

5

4

3

2

1

0

USBEN

UADD6

UADD5

UADD4

UADD3

UADD2

UADD1

UADD0

Bit

Symbol

R/W

Function

7

USBEN

R/W

USB Function Enable Bit.

When USBEN is clear, the USB module will not respond to any tokens

from host.

RESET clears this bit.

6 to 0

UADD6 to

UADD0

R/W

Specify the USB address of the device.

RESET clears these bits.