Table 65. description of the uista bits – ST & T UPSD3212C User Manual

Page 78

uPSD3212A, uPSD3212C, uPSD3212CV

78/163

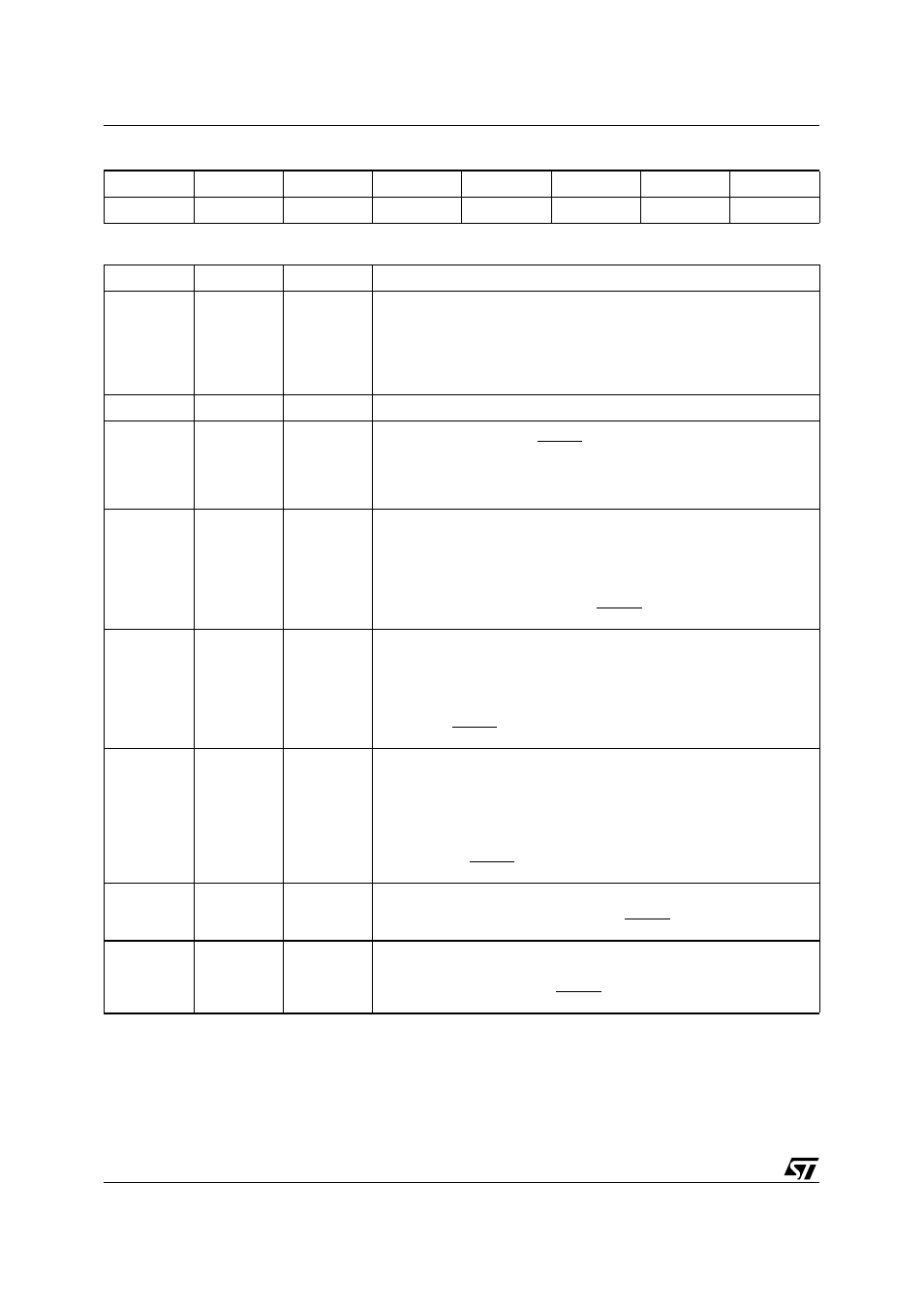

Table 64. USB Interrupt Status Register (UISTA: 0E8h)

Table 65. Description of the UISTA Bits

7

6

5

4

3

2

1

0

SUSPND

—

RSTF

TXD0F

RXD0F

TXD1F

EOPF

RESUMF

Bit

Symbol

R/W

Function

7

SUSPND

R/W

USB Suspend Mode Flag.

To save power, this bit should be set if a 3ms constant idle state is

detected on USB bus. Setting this bit stops the clock to the USB and

causes the USB module to enter Suspend Mode. Software must clear

this bit after the Resume flag (RESUMF) is set while this Resume

Interrupt Flag is serviced

6

—

—

Reserved

5

RSTF

R

USB Reset Flag.

This bit is set when a valid RESET signal state is detected on the D+ and

D- lines. When the RSTE bit in the UIEN Register is set, this reset

detection will also generate an internal reset signal to reset the CPU and

other peripherals including the USB module.

4

TXD0F

R/W

Endpoint0 Data Transmit Flag.

This bit is set after the data stored in Endpoint 0 transmit buffers has

been sent and an ACK handshake packet from the host is received.

Once the next set of data is ready in the transmit buffers, software must

clear this flag. To enable the next data packet transmission, TX0E must

also be set. If TXD0F Bit is not cleared, a NAK handshake will be

returned in the next IN transactions. RESET clears this bit.

3

RXD0F

R/W

Endpoint0 Data Receive Flag.

This bit is set after the USB module has received a data packet and

responded with ACK handshake packet. Software must clear this flag

after all of the received data has been read. Software must also set

RX0E Bit to one to enable the next data packet reception. If RXD0F Bit is

not cleared, a NAK handshake will be returned in the next OUT

transaction. RESET clears this bit.

2

TXD1F

R/W

Endpoint1 / Endpoint2 Data Transmit Flag.

This bit is shared by Endpoints 1 and Endpoints 2. It is set after the data

stored in the shared Endpoint 1/ Endpoint 2 transmit buffer has been sent

and an ACK handshake packet from the host is received. Once the next

set of data is ready in the transmit buffers, software must clear this flag.

To enable the next data packet transmission, TX1E must also be set. If

TXD1F Bit is not cleared, a NAK handshake will be returned in the next

IN transaction. RESET clears this bit.

1

EOPF

R/W

End of Packet Flag.

This bit is set when a valid End of Packet sequence is detected on the D+

and D-line. Software must clear this flag. RESET clears this bit.

0

RESUMF

R/W

Resume Flag.

This bit is set when USB bus activity is detected while the SUSPND Bit is

set.

Software must clear this flag. RESET clears this bit.