Standard jtag signals, Table 103. jtag port signals, Jtag extensions – ST & T UPSD3212C User Manual

Page 127: Security and flash memory protection, Initial delivery state, Programming in-cir, Programming

127/163

uPSD3212A, uPSD3212C, uPSD3212CV

PROGRAMMING IN-CIRCUIT USING THE JTAG SERIAL INTERFACE

The JTAG Serial Interface pins (TMS, TCK, TDI,

TDO) are dedicated pins on Port C (see Table

). All memory blocks (primary and secondary

Flash memory), PLD logic, and PSD MODULE

Configuration Register Bits may be programmed

through the JTAG Serial Interface block. A blank

device can be mounted on a printed circuit board

and programmed using JTAG.

The standard JTAG signals (IEEE 1149.1) are

TMS, TCK, TDI, and TDO. Two additional signals,

TSTAT and TERR, are optional JTAG extensions

used to speed up Program and Erase cycles.

By default, on a blank device (as shipped from the

factory or after erasure), four pins on Port C are

the basic JTAG signals TMS, TCK, TDI, and TDO

.

Standard JTAG Signals

At power-up, the standard JTAG pins are inputs,

waiting for a JTAG serial command from an exter-

nal JTAG controller device (such as FlashLINK or

Automated Test Equipment). When the enabling

command is received, TDO becomes an output

and the JTAG channel is fully functional. The

same command that enables the JTAG channel

may optionally enable the two additional JTAG sig-

nals, TSTAT and TERR.

The RESET input to the uPS3200 should be active

during JTAG programming. The active RESET

puts the MCU module into RESET Mode while the

PSD Module is being programmed. See Applica-

tion Note AN1153 for more details on JTAG In-

System Programming (ISP).

The uPSD321x Devices supports JTAG In-Sys-

tem-Configuration (ISC) commands, but not

Boundary Scan. The PSDsoft Express software

tool and FlashLINK JTAG programming cable im-

plement the JTAG In-System-Configuration (ISC)

commands.

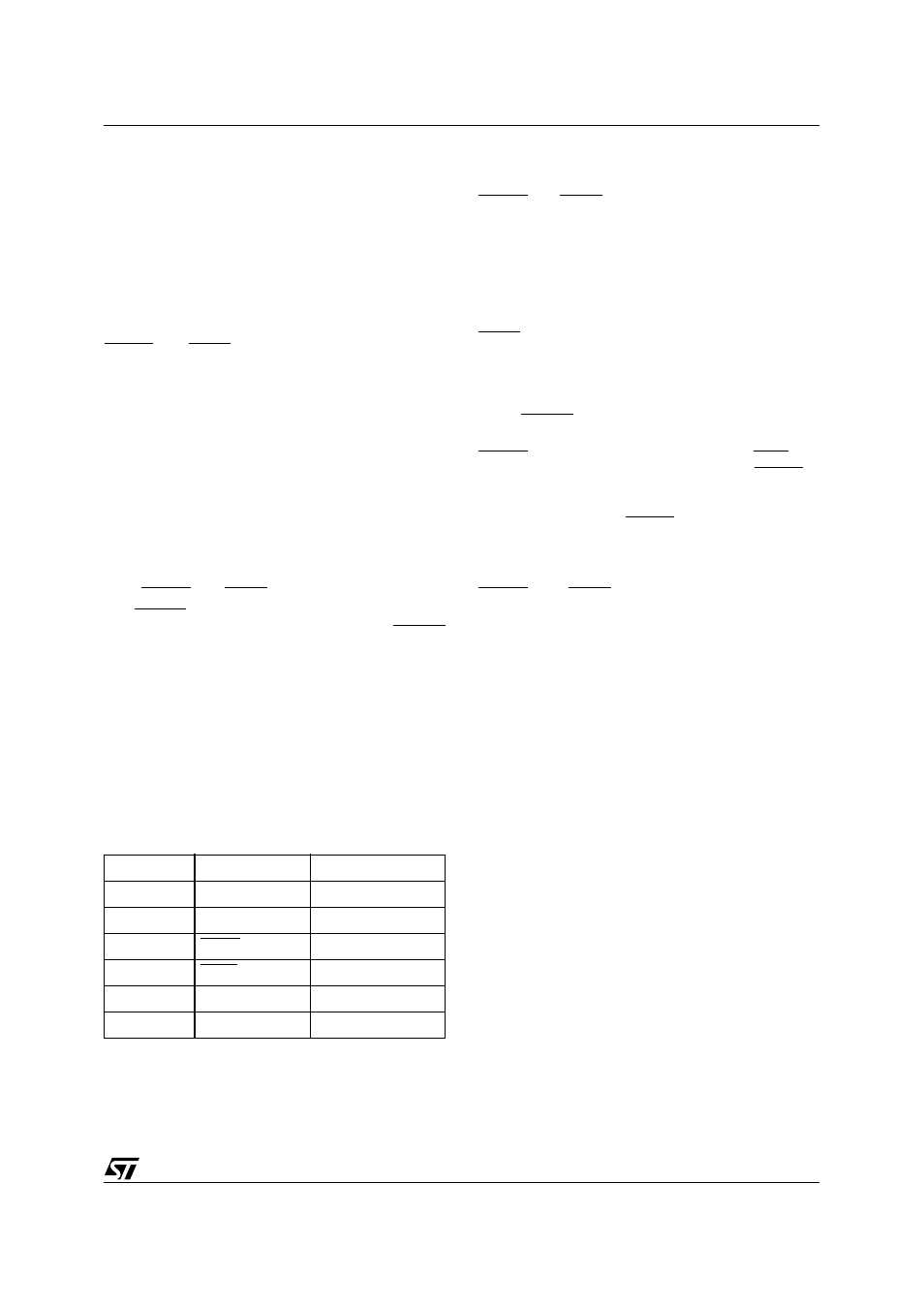

Table 103. JTAG Port Signals

JTAG Extensions

TSTAT and TERR are two JTAG extension signals

enabled by an “ISC_ENABLE” command received

over the four standard JTAG signals (TMS, TCK,

TDI, and TDO). They are used to speed Program

and Erase cycles by indicating status on uPDS

signals instead of having to scan the status out se-

rially using the standard JTAG channel. See Appli-

cation Note

AN1153

.

TERR indicates if an error has occurred when

erasing a sector or programming a byte in Flash

memory. This signal goes Low (active) when an

Error condition occurs, and stays Low until an

“ISC_CLEAR” command is executed or a chip Re-

set (RESET) pulse is received after an

“ISC_DISABLE” command.

TSTAT behaves the same as Ready/Busy de-

scribed in

. TSTAT is

High when the PSD MODULE device is in READ

Mode (primary and secondary Flash memory con-

tents can be read). TSTAT is Low when Flash

memory Program or Erase cycles are in progress,

and also when data is being written to the second-

ary Flash memory.

TSTAT and TERR can be configured as “open

drain” type signals during an “ISC_ENABLE” com-

mand.

Security and Flash memory Protection

When the Security Bit is set, the device cannot be

read on a Device Programmer or through the

JTAG Port. When using the JTAG Port, only a Full

Chip Erase command is allowed.

All other Program, Erase and Verify commands

are blocked. Full Chip Erase returns the part to a

non-secured blank state. The Security Bit can be

set in PSDsoft Express Configuration.

All primary and secondary Flash memory sectors

can individually be sector protected against era-

sures. The sector protect bits can be set in PSD-

soft Express Configuration.

INITIAL DELIVERY STATE

When delivered from ST, the uPSD321x Devices

have all bits in the memory and PLDs set to '1.'

The code, configuration, and PLD logic are loaded

using the programming procedure. Information for

programming the device is available directly from

ST. Please contact your local sales representa-

tive.

Port C Pin

JTAG Signals

Description

PC0

TMS

Mode Select

PC1

TCK

Clock

PC3

TSTAT

Status (optional)

PC4

TERR

Error Flag (optional)

PC5

TDI

Serial Data In

PC6

TDO

Serial Data Out