Figure 81. reset (reset) timing, Table 137. reset (reset) timing (5v devices), Table 138. reset (reset) timing (3v devices) – ST & T UPSD3212C User Manual

Page 153: Table 139. vstbyon definitions timing (5v devices), Table 140. vstbyon timing (3v devices)

153/163

uPSD3212A, uPSD3212C, uPSD3212CV

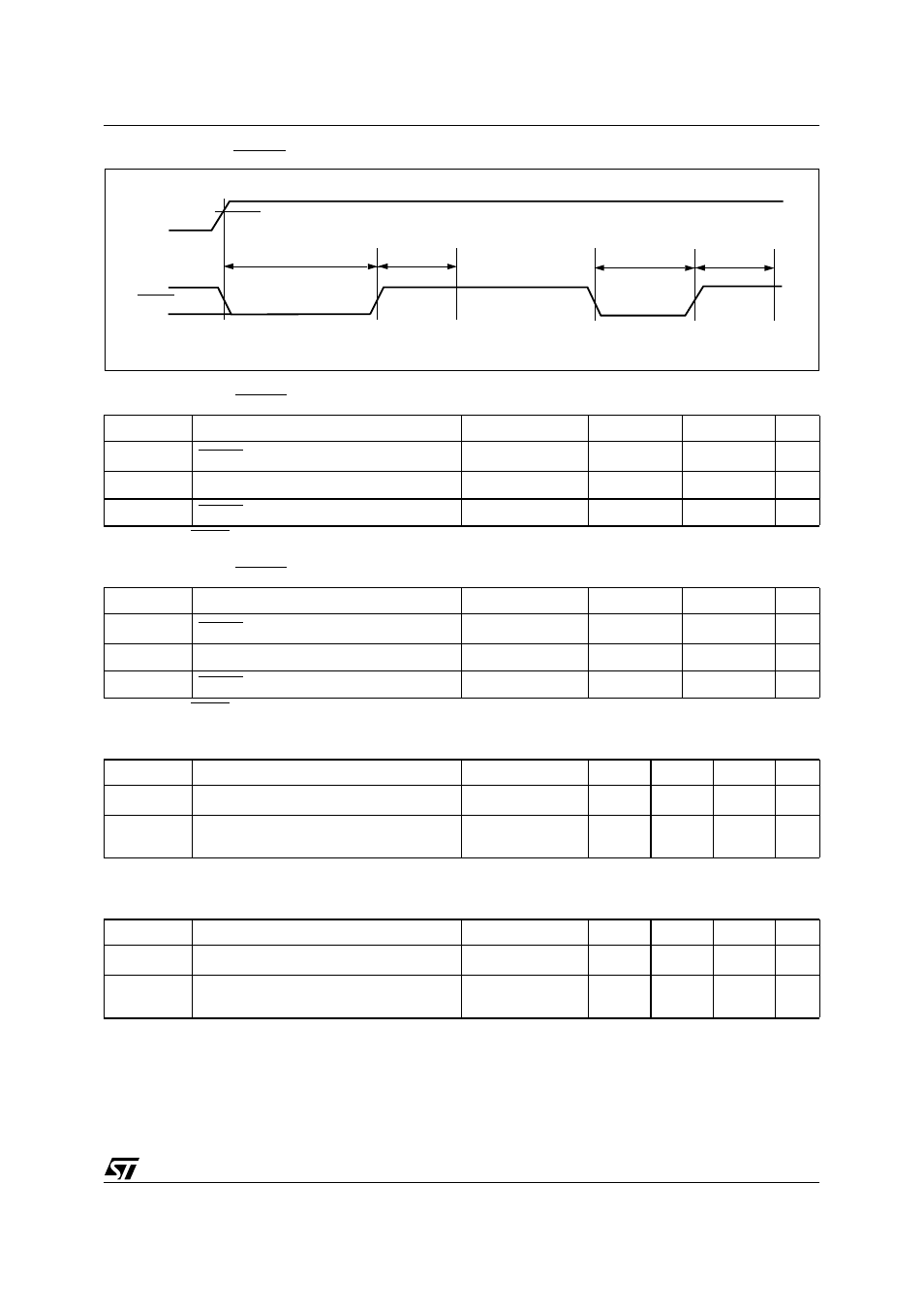

Figure 81. Reset (RESET) Timing

Table 137. Reset (RESET) Timing (5V Devices)

Note: 1. Reset (RESET) does not reset Flash memory Program or Erase cycles.

Table 138. Reset (RESET) Timing (3V Devices)

Note: 1. Reset (RESET) does not reset Flash memory Program or Erase cycles.

Table 139. V

STBYON

Definitions Timing (5V Devices)

Note: 1. V

STBYON

timing is measured at V

CC

ramp rate of 2ms.

Table 140. V

STBYON

Timing (3V Devices)

Note: 1. V

STBYON

timing is measured at V

CC

ramp rate of 2ms.

Symbol

Parameter

Conditions

Min

Max

Unit

t

NLNH

RESET Active Low Time

(1)

150

ns

t

NLNH–PO

Power-on Reset Active Low Time

1

ms

t

OPR

RESET High to Operational Device

120

ns

Symbol

Parameter

Conditions

Min

Max

Unit

t

NLNH

RESET Active Low Time

(1)

300

ns

t

NLNH–PO

Power-on Reset Active Low Time

1

ms

t

OPR

RESET High to Operational Device

300

ns

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

t

BVBH

V

STBY

Detection to V

STBYON

Output High

(Note

1)

20

µs

t

BXBL

V

STBY

Off Detection to V

STBYON

Output

Low

(Note

1)

20

µs

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

t

BVBH

V

STBY

Detection to V

STBYON

Output High

(Note

1)

20

µs

t

BXBL

V

STBY

Off Detection to V

STBYON

Output

Low

(Note

1)

20

µs

tNLNH-PO

tOPR

AI07437

RESET

tNLNH

tOPR

V

CC

V

CC

(min)

Power-On Reset

Warm Reset