Machine cycles, Table 14. conditional jump instructions – ST & T UPSD3212C User Manual

Page 25

25/163

uPSD3212A, uPSD3212C, uPSD3212CV

Table

shows the list of conditional jumps avail-

able to the uPSD321x Devices user. All of these

jumps specify the destination address by the rela-

tive offset method, and so are limited to a jump dis-

tance of -128 to +127 bytes from the instruction

following the conditional jump instruction. Impor-

tant to note, however, the user specifies to the as-

sembler the actual destination address the same

way as the other jumps: as a label or a 16-bit con-

stant.

There is no Zero Bit in the PSW. The JZ and JNZ

instructions test the Accumulator data for that con-

dition.

The DJNZ instruction (Decrement and Jump if Not

Zero) is for loop control. To execute a loop N

times, load a counter byte with N and terminate the

loop with a DJNZ to the beginning of the loop, as

shown below for N = 10:

MOV COUNTER,#10

LOOP: (begin loop)

•

•

•

(end loop)

DJNZ COUNTER, LOOP

(continue)

The CJNE instruction (Compare and Jump if Not

Equal) can also be used for loop control as in

. Two bytes are specified in the op-

erand field of the instruction. The jump is executed

only if the two bytes are not equal. In the example

of

Shifting a BCD Number One

Digits to the Right, the two bytes were data in R1

and the constant 2Ah. The initial data in R1 was

2Eh.

Every time the loop was executed, R1 was decre-

mented, and the looping was to continue until the

R1 data reached 2Ah.

Another application of this instruction is in “greater

than, less than” comparisons. The two bytes in the

operand field are taken as unsigned integers. If the

first is less than the second, then the Carry Bit is

set (1). If the first is greater than or equal to the

second, then the Carry Bit is cleared.

Machine Cycles

A machine cycle consists of a sequence of six

states, numbered S1 through S6. Each state time

lasts for two oscillator periods. Thus, a machine

cycle takes 12 oscillator periods or 1µs if the oscil-

lator frequency is 12MHz. Refer to

Each state is divided into a Phase 1 half and a

Phase 2 half. State Sequence in uPSD321x Devic-

es shows that retrieve/execute sequences in

states and phases for various kinds of instructions.

Normally two program retrievals are generated

during each machine cycle, even if the instruction

being executed does

not

require it. If the instruc-

tion being executed does not need more code

bytes, the CPU simply ignores the extra retrieval,

and the Program Counter is not incremented.

Execution of a one-cycle instruction (

) begins during State 1 of the machine

cycle, when the opcode is latched into the Instruc-

tion Register. A second retrieve occurs during S4

of the same machine cycle. Execution is complete

at the end of State 6 of this machine cycle.

The MOVX instructions take two machine cycles

to execute. No program retrieval is generated dur-

ing the second cycle of a MOVX instruction. This

is the only time program retrievals are skipped.

The retrieve/execute sequence for MOVX instruc-

tion is shown in

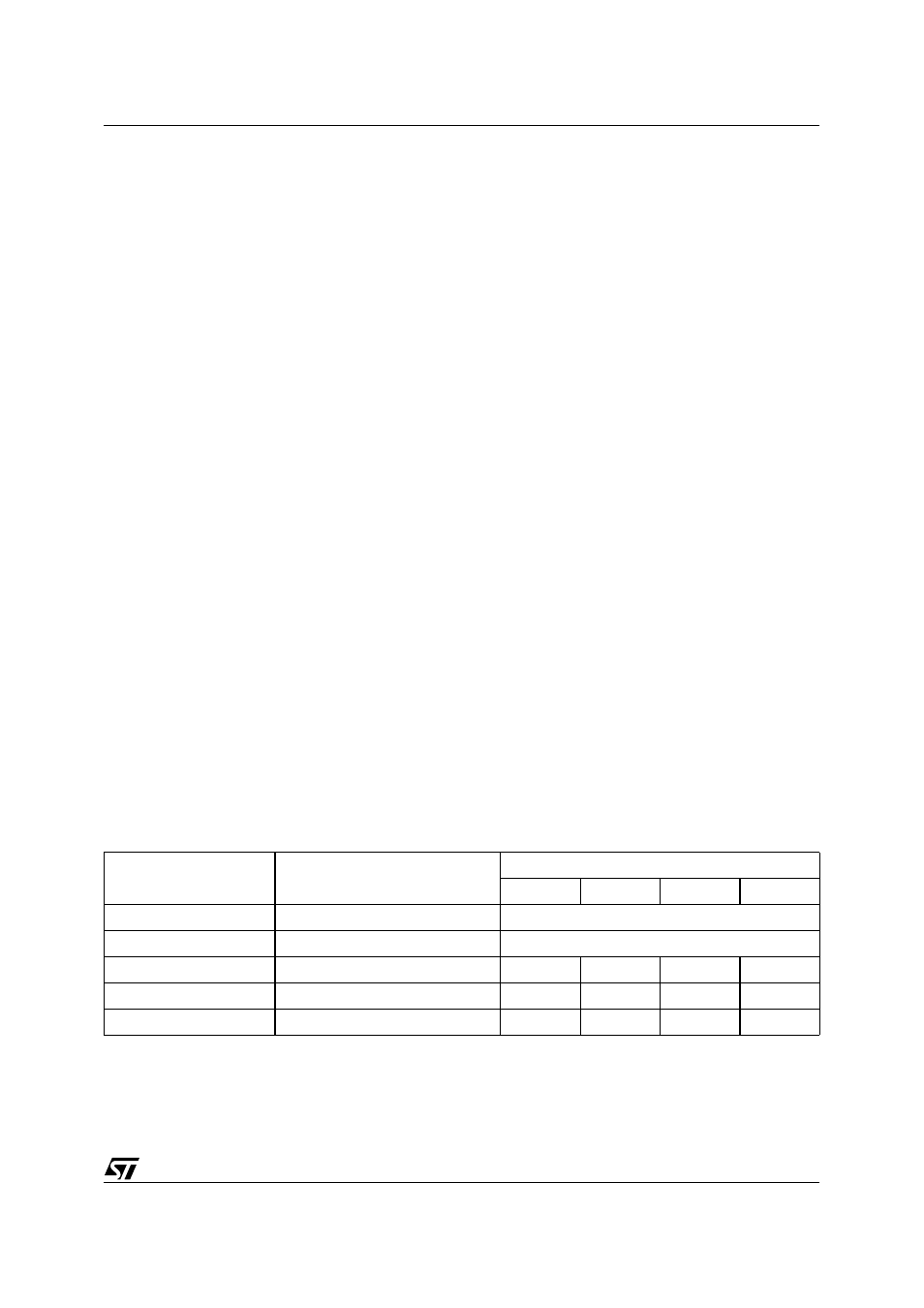

Table 14. Conditional Jump Instructions

Mnemonic

Operation

Addressing Modes

Dir.

Ind.

Reg.

Imm

JZ rel

Jump if A = 0

Accumulator only

JNZ rel

Jump if A

≠

0

Accumulator only

DJNZ

Decrement and jump if not zero

X

X

CJNE A,

Jump if A

≠

X

X

CJNE

Jump if

≠

#data

X

X