Boolean instructions, Relative offset, Table 12. boolean instructions – ST & T UPSD3212C User Manual

Page 23

23/163

uPSD3212A, uPSD3212C, uPSD3212CV

Boolean Instructions

The uPSD321x Devices contain a complete Bool-

ean (single-bit) processor. One page of the inter-

nal RAM contains 128 addressable bits, and the

SFR space can support up to 128 addressable bits

as well. All of the port lines are bit-addressable,

and each one can be treated as a separate single-

bit port. The instructions that access these bits are

not just conditional branches, but a complete

menu of move, set, clear, complement, OR and

AND instructions. These kinds of bit operations

are not easily obtained in other architectures with

any amount of byte-oriented software.

The instruction set for the Boolean processor is

shown in Table

. All bits accesses are by direct

addressing.

Bit addresses 00h through 7Fh are in the Lower

128, and bit addresses 80h through FFh are in

SFR space.

Note how easily an internal flag can be moved to

a port pin:

MOV C,FLAG

MOV P1.0,C

In this example, FLAG is the name of any addres-

sable bit in the Lower 128 or SFR space. An I/O

line (the LSB of Port 1, in this case) is set or

cleared depending on whether the Flag Bit is '1' or

'0.'

The Carry Bit in the PSW is used as the single-bit

Accumulator of the Boolean processor. Bit instruc-

tions that refer to the Carry Bit as C assemble as

Carry-specific instructions (CLR C, etc.). The Car-

ry Bit also has a direct address, since it resides in

the PSW register, which is bit-addressable.

Note: The Boolean instruction set includes ANL

and ORL operations, but not the XRL (Exclusive

OR) operation. An XRL operation is simple to im-

plement in software. Suppose, for example, it is re-

quired to form the Exclusive OR of two bits:

C = bit 1 .XRL. bit2

The software to do that could be as follows:

MOV C , bit1

JNB bit2, OVER

CPL C

OVER: (continue)

First, Bit 1 is moved to the Carry. If bit2 = 0, then

C now contains the correct result. That is, Bit 1

.XRL. bit2 = bit1 if bit2 = 0. On the other hand, if

bit2 = 1, C now contains the complement of the

correct result. It need only be inverted (CPL C) to

complete the operation.

This code uses the JNB instruction, one of a series

of bit-test instructions which execute a jump if the

addressed bit is set (JC, JB, JBC) or if the ad-

dressed bit is not set (JNC, JNB). In the above

case, Bit 2 is being tested, and if bit2 = 0, the CPL

C instruction is jumped over.

JBC executes the jump if the addressed bit is set,

and also clears the bit. Thus a flag can be tested

and cleared in one operation. All the PSW bits are

directly addressable, so the Parity Bit, or the gen-

eral-purpose flags, for example, are also available

to the bit-test instructions.

Relative Offset

The destination address for these jumps is speci-

fied to the assembler by a label or by an actual ad-

dress in Program memory. How-ever, the

destination address assembles to a relative offset

byte. This is a signed (two’s complement) offset

byte which is added to the PC in two’s complement

arithmetic if the jump is executed.

The range of the jump is therefore -128 to +127

Program Memory bytes relative to the first byte fol-

lowing the instruction.

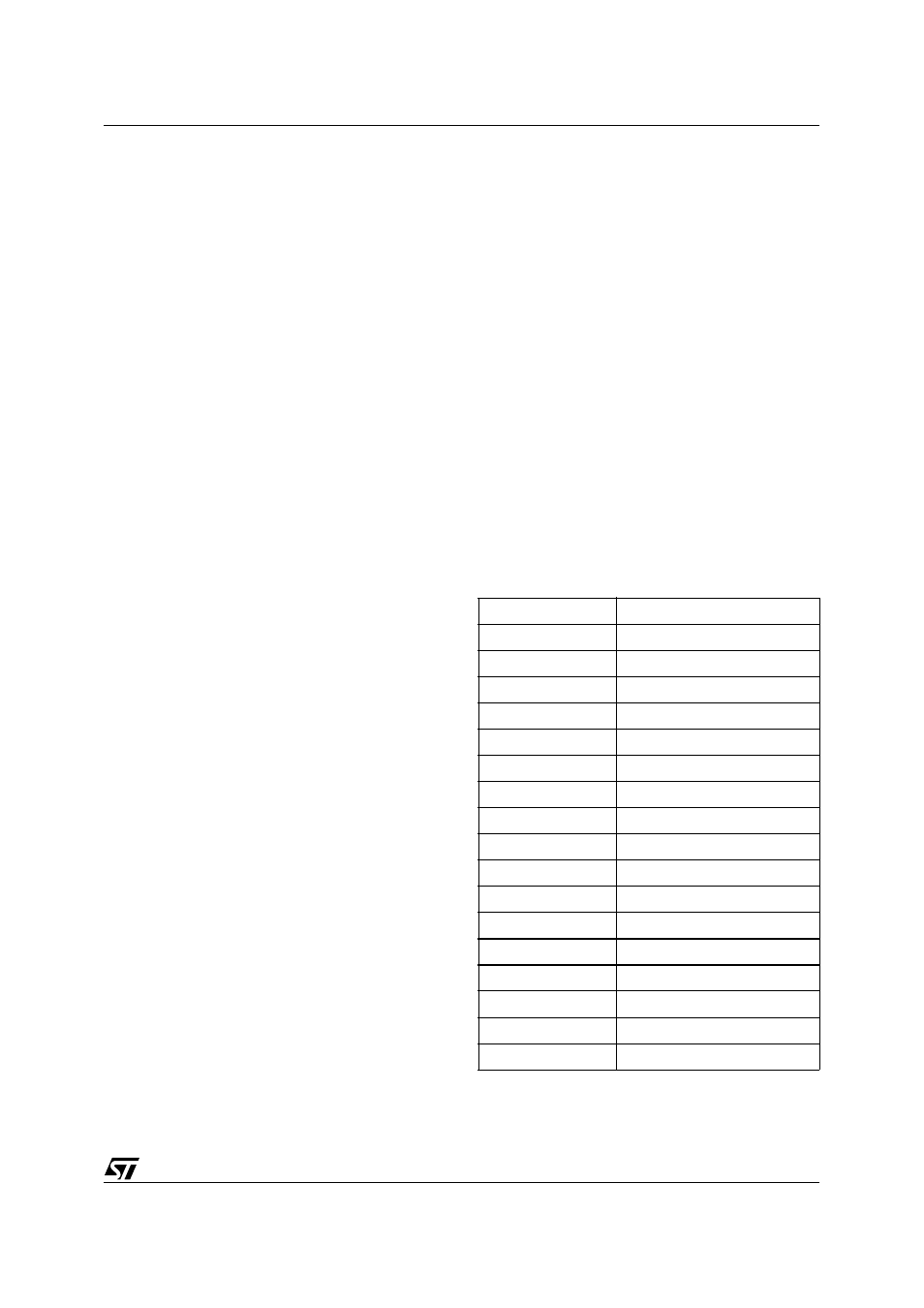

Table 12. Boolean Instructions

Mnemonic

Operation

ANL C,bit

C = A .AND. bit

ANL C,/bit

C = C .AND. .NOT. bit

ORL C,bit

C = A .OR. bit

ORL C,/bit

C = C .OR. .NOT. bit

MOV C,bit

C = bit

MOV bit,C

bit = C

CLR C

C = 0

CLR bit

bit = 0

SETB C

C = 1

SETB bit

bit = 1

CPL C

C = .NOT. C

CPL bit

bit = .NOT. bit

JC rel

Jump if C =1

JNC rel

Jump if C = 0

JB bit,rel

Jump if bit =1

JNB bit,rel

Jump if bit = 0

JBC bit,rel

Jump if bit = 1; CLR bit