Table 70. usb control register (ucon2: 0ech), Table 71. description of the ucon2 bits, Table 73. description of the usta bits – ST & T UPSD3212C User Manual

Page 81

81/163

uPSD3212A, uPSD3212C, uPSD3212CV

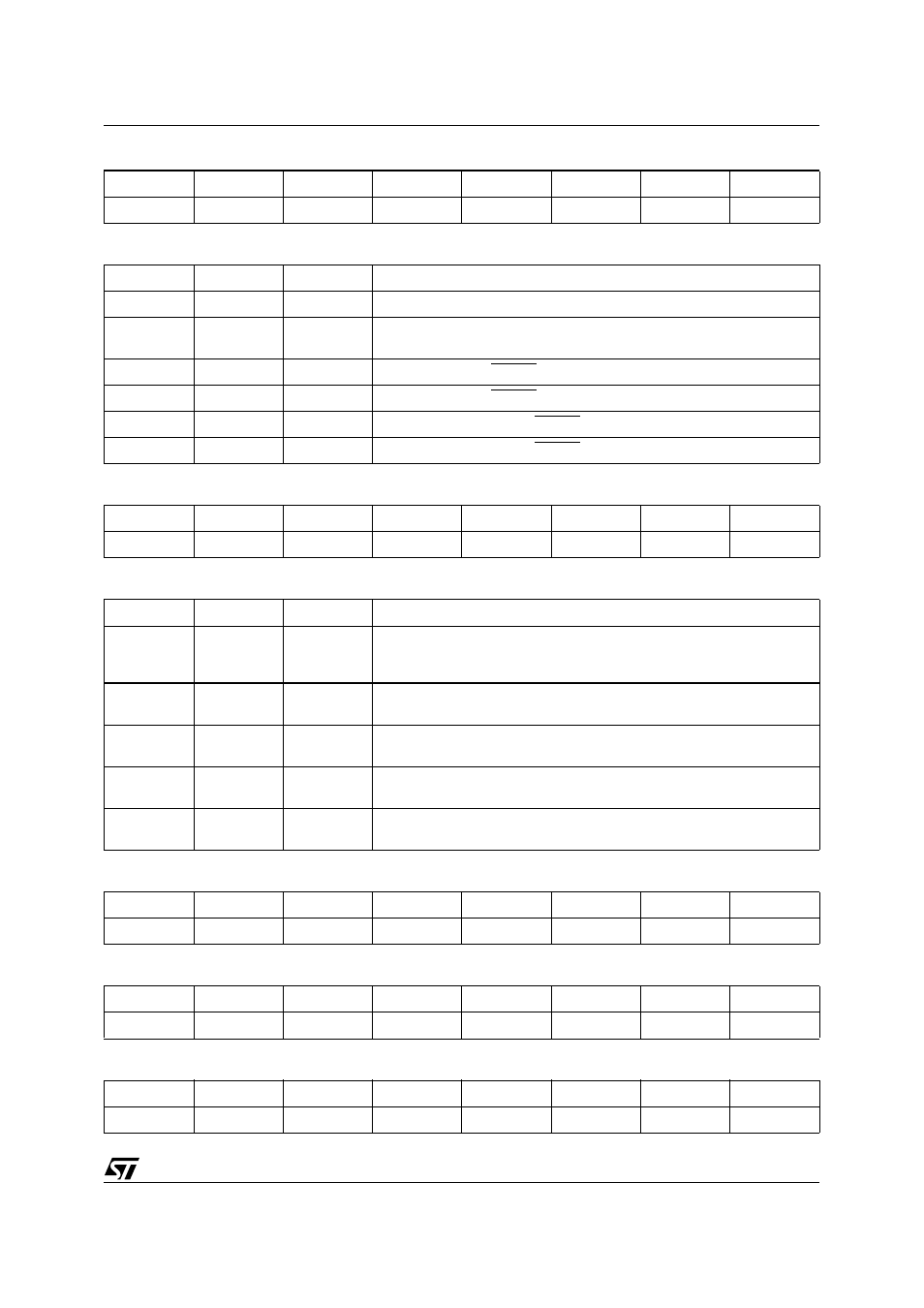

Table 70. USB Control Register (UCON2: 0ECh)

Table 71. Description of the UCON2 Bits

Table 72. USB Endpoint0 Status Register (USTA: 0EDh)

Table 73. Description of the USTA Bits

Table 74. USB Endpoint0 Data Receive Register (UDR0: 0EFh)

Table 75. USB Endpoint0 Data Transmit Register (UDT0: 0E7h)

Table 76. USB Endpoint1 Data Transmit Register (UDT1: 0E6h)

7

6

5

4

3

2

1

0

—

—

—

SOUT

EP2E

EP1E

STALL2

STALL1

Bit

Symbol

R/W

Function

7 to 5

—

—

Reserved

4

SOUT

R/W

Status out is used to automatically respond to the OUT of a control

READ transfer

3

EP2E

R/W

Endpoint2 enable. RESET clears this bit

2

EP1E

R/W

Endpoint1 enable. RESET clears this bit

1

STALL2

R/W

Endpoint2 Force Stall Bit. RESET clears this bit

0

STALL1

R/W

Endpoint1 Force Stall Bit. RESET clears this bit

7

6

5

4

3

2

1

0

RSEQ

SETUP

IN

OUT

RP0SIZ3

RP0SIZ2

RP0SIZ1

RP0SIZ0

Bit

Symbol

R/W

Function

7

RSEQ

R/W

Endpoint0 receive data packet PID. (0=DATA0, 1=DATA1)

This bit will be compared with the type of data packet last received for

Endpoint0

6

SETUP

R

SETUP Token Detect Bit. This bit is set when the received token packet

is a SEPUP token, PID = b1101.

5

IN

R

IN Token Detect Bit.

This bit is set when the received token packet is an IN token.

4

OUT

R

OUT Token Detect Bit.

This bit is set when the received token packet is an OUT token.

3 to 0

RP0SIZ3 to

RP0SIZ0

R

The number of data bytes received in a DATA packet

7

6

5

4

3

2

1

0

UDR0.7

UDR0.6

UDR0.5

UDR0.4

UDR0.3

UDR0.2

UDR0.1

UDR0.0

7

6

5

4

3

2

1

0

UDT0.7

UDT0.6

UDT0.5

UDT0.4

UDT0.3

UDT0.2

UDT0.1

UDT0.0

7

6

5

4

3

2

1

0

UDT1.7

UDT1.6

UDT1.5

UDT1.4

UDT1.3

UDT1.2

UDT1.1

UDT1.0