2 interface signal groups, Figure 4. interface signals, Interface signal groups – Intel IXF1104 User Manual

Page 38: Interface signals, Intel, Ixf1104 media access controller

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet

38

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

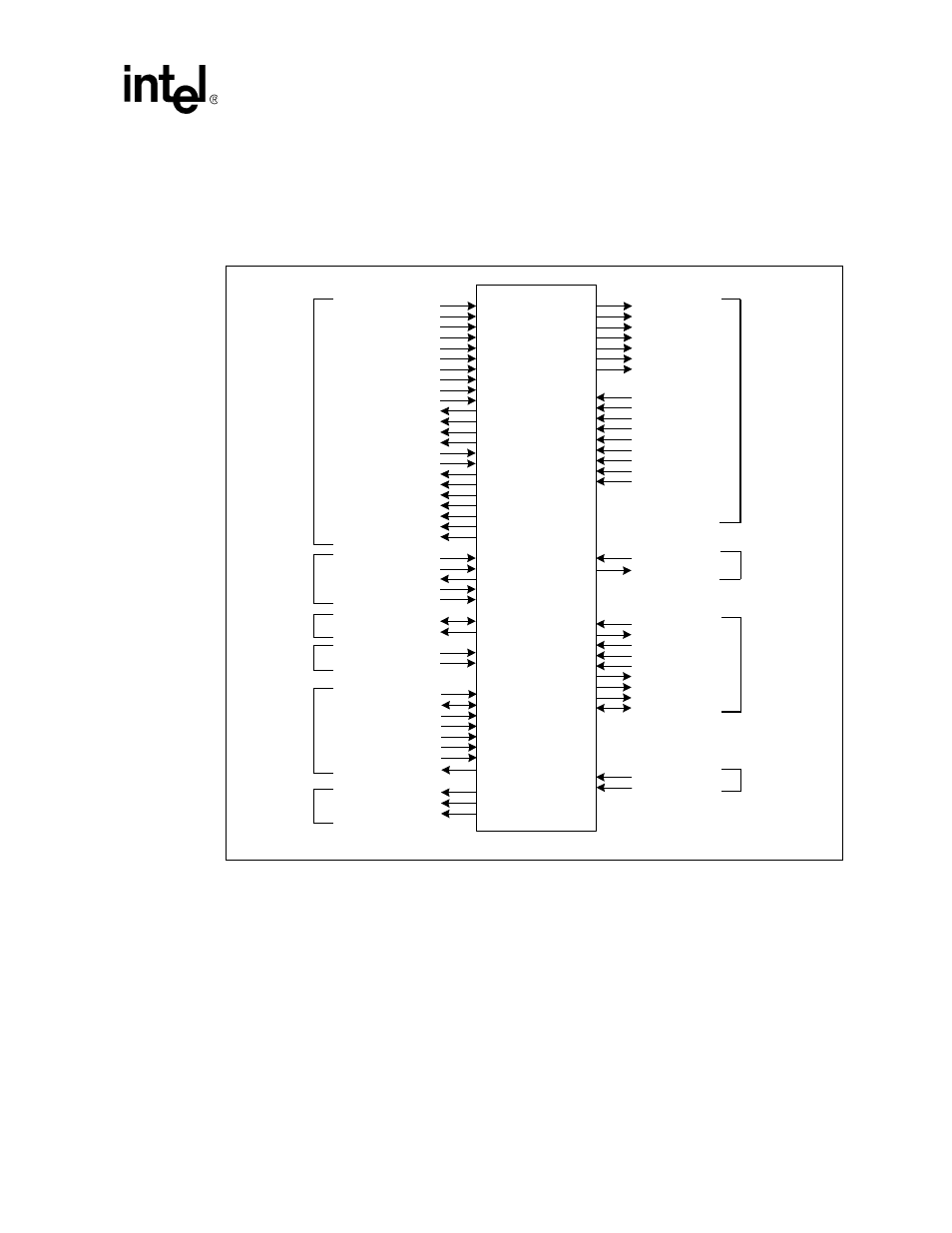

4.2

Interface Signal Groups

This section describes the IXF1104 MAC signals in groups according to the associated interface or

function.

shows the various interfaces available on the IXF1104 MAC.

Figure 4. Interface Signals

TDAT[ 31:0]

TFCLK

TEN B_0

TER R_0

TPRTY_0

TMOD [1: 0]

TSX

TSOP_0

TEOP_0

TADR [1: 0]

DTPA_0:3

STPA

PTPA

R D AT[ 31: 0]

RFCLK

R EN B_0

R VAL_0

R ER R _0

RPRTY_0

RMOD [1: 0]

RSX

R SOP_0

R EOP_0

TMS

TD I

TD O

TCLK

MDI O

MD C

TXPAUSEADD [2: 0]

TXPAUSEFR

U PX_WID TH [1: 0]

UPX_D ATA[ 31:0]

U PX_AD D[ 10: 0]

U PX_BADD [1: 0]

U PX_WR_L

U PX_R D_L

U PX_C S_L

U PX_RD Y_L

LED_CLK

LED _D ATA

LED_LATCH

SYS_RES_L

CLK125

MOD _DEF_0:3

TX_D ISABLE_0:3

TX_FAU LT_0:3

RX_LOS_0:3

TX_FAU LT_IN T

RX_LOS_IN T

MOD _DEF_IN T

I

2

C _C LK

I

2

C _D ATA_0:3

SPI3

I nterface

JTA G

I nterface

MDI O

I nterface

Pause

Control

I nterface

CPU

I nterface

LED

I nterface

System

Interface

GMII

RGMII

GMII and

R GMII

Interfaces*

* D at a and clock balls are shared for

GMII and RGMI I Interf aces

SerD es

Interface

Optical

Module

Interface

Si gnals*

*

** These optical module signals

are mult iplexed on the GMII balls.

RX_P/N_0:3

TX_P/N_0:3

TRST_L

Intel

®

IXF1104

Media Access

Controller

B3181-01

MPHY

SPHY

TFCLK

TENB_0: 3

TERR _0: 3

TPR TY_0: 3

TSOP_0:3

TEOP_0:3

TDAT[ 7:0] _0: 3

TADR [1:0]

DTPA_0: 3

PTPA

R DAT[ 7:0] _0: 3

RFCLK

RENB_0: 3

RVAL_0: 3

RERR _0: 3

R PR TY_0: 3

RSOP_0: 3

REOP_0: 3

TXC_0:3

TXD[ 7:0] _3

TXC _0: 3

TD[3:0] _3

TXD[ 7:0] _2

TD[3:0] _2

TXD[ 7:0] _1

TD[3:0] _1

TXD[ 7:0] _0

TD[3:0] _0

TX_EN_0:3

TX_ER_0:3

TX_C TL_0: 3

RXC_0:3

R XC _0: 3

RXD[ 7:0]_3

R D[ 3:0] _3

RXD[ 7:0]_2

R D[ 3:0] _2

RXD[ 7:0]_1

R D[ 3:0] _1

RXD[ 7:0]_0

R D[ 3:0] _0

RX_D V_0:3

RX_ER_0:3

CR S_0:3

COL_0:3

R X_CTL_0:3