1 transmitter operational overview, 2 transmitter programmable driver-power levels, Table 29. serdes driver tx power levels – Intel IXF1104 User Manual

Page 104: Transmitter operational overview, Transmitter programmable driver-power levels, Serdes driver tx power levels

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet

104

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

speed SerDes and are capable of operating in either an AC- or DC-coupled environment. AC

coupling is recommended for this interface to ensure that the correct input bias current is supplied

at the receiver.

The SerDes receive interface receives serialized data at 1.25 GHz. The interface is differential with

two signals for the receive operation. The equalizer receives a differential signal that is equalized

for the assumed media channel.

The SerDes transmit and receive interfaces are designed to operate

within a 100

Ω differential environment and all terminations are included on the device. The

SerDes is capable of operating in either AC- or DC-coupled environments.

5.6.2.1

Transmitter Operational Overview

The transmit section of the IXF1104 MAC has to serialize the Ten Bit Interface (TBI) data from the

IXF1104 MAC MAC section and outputs this data at 1.25 GHz differential signal levels. The

1.25 GHz differential SerDes signals are compliant with the Small Form Factor Pluggable (SFP)

Multi-Source Agreement (MSA).

The transmitter section takes the contents of the data register within the MAC and synchronously

transfers the data out, ten bits at a time – Least Significant Bit (LSB) first, followed by the next

Most Significant Bit (MSB). When these ten bits have been serialized and transmitted, the next

word of 10-bit data from the MAC is ready to be serialized for transmission.

The data is transmitted by the high-speed current mode differential SerDes output stage using an

internal 1.25 GHz clock generated from the 125 MHz clock input.

5.6.2.2

Transmitter Programmable Driver-Power Levels

The IXF1104 MAC SerDes core has programmable transmitter power levels to enhance usability

in any given application.The SerDes Registers are programmable to allow adjustment of the

transmit core driver output power. When driving a 100

Ω differential terminated network, these

output power settings effectively establish the differential voltage swings at the driver output.

The

“TX Driver Power Level Ports 0 - 3 ($0x784)"

allows the selection of four discrete power

settings. The selected power setting of these inputs is applied to each of the transmit core drivers on

a per-port basis.

Table 29 “SerDes Driver TX Power Levels”

lists the

normalized power settings of

the transmit drivers as a function of the Driver Power Control inputs. The normalized current

setting is 10 mA, which corresponds to the normalized power setting of 1.0. This is the default

setting of the IXF1104 MAC SerDes interface. Other values listed in the Normalized Driver Power

Setting column are multiples of 10 mA. For example, with inputs at 1110, the driver power is the

following:

.5 x 10 mA = 5 mA.

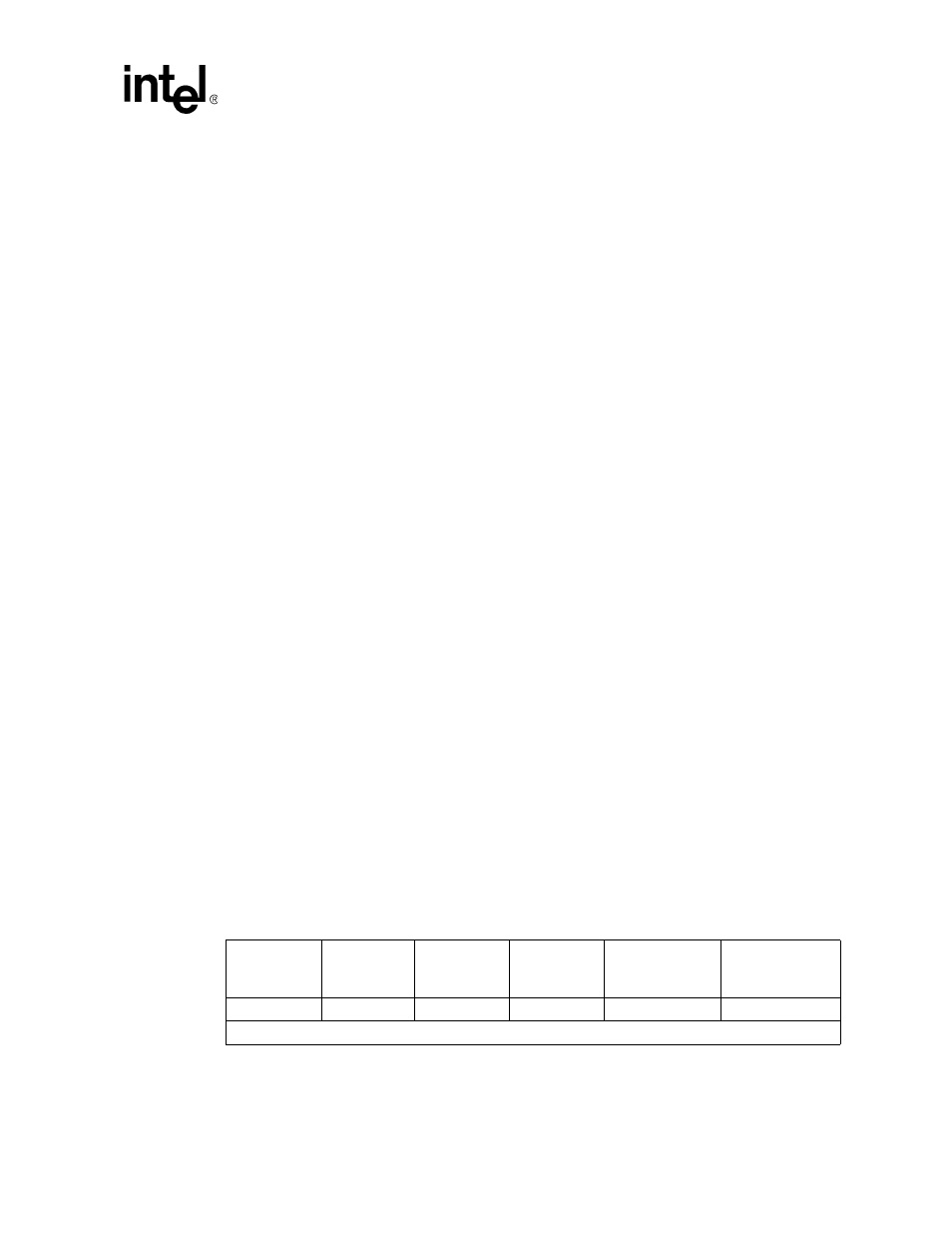

Table 29. SerDes Driver TX Power Levels

DRVPWRx[3]

DRVPWRx[2]

DRVPWRx[1]

DRVPWRx[0]

Normalized

Driver Power

Setting

Driver Power

0

0

1

1

1.33

13.3 mA

NOTE: All other values are reserved.