Clock and interface mode change enable ports 0 - 3, Clock and interface, Mode change enable ports 0 - 3 ($0x794) – Intel IXF1104 User Manual

Page 221: Clock and, Interface mode change enable ports 0 - 3 ($0x794)

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

221

Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

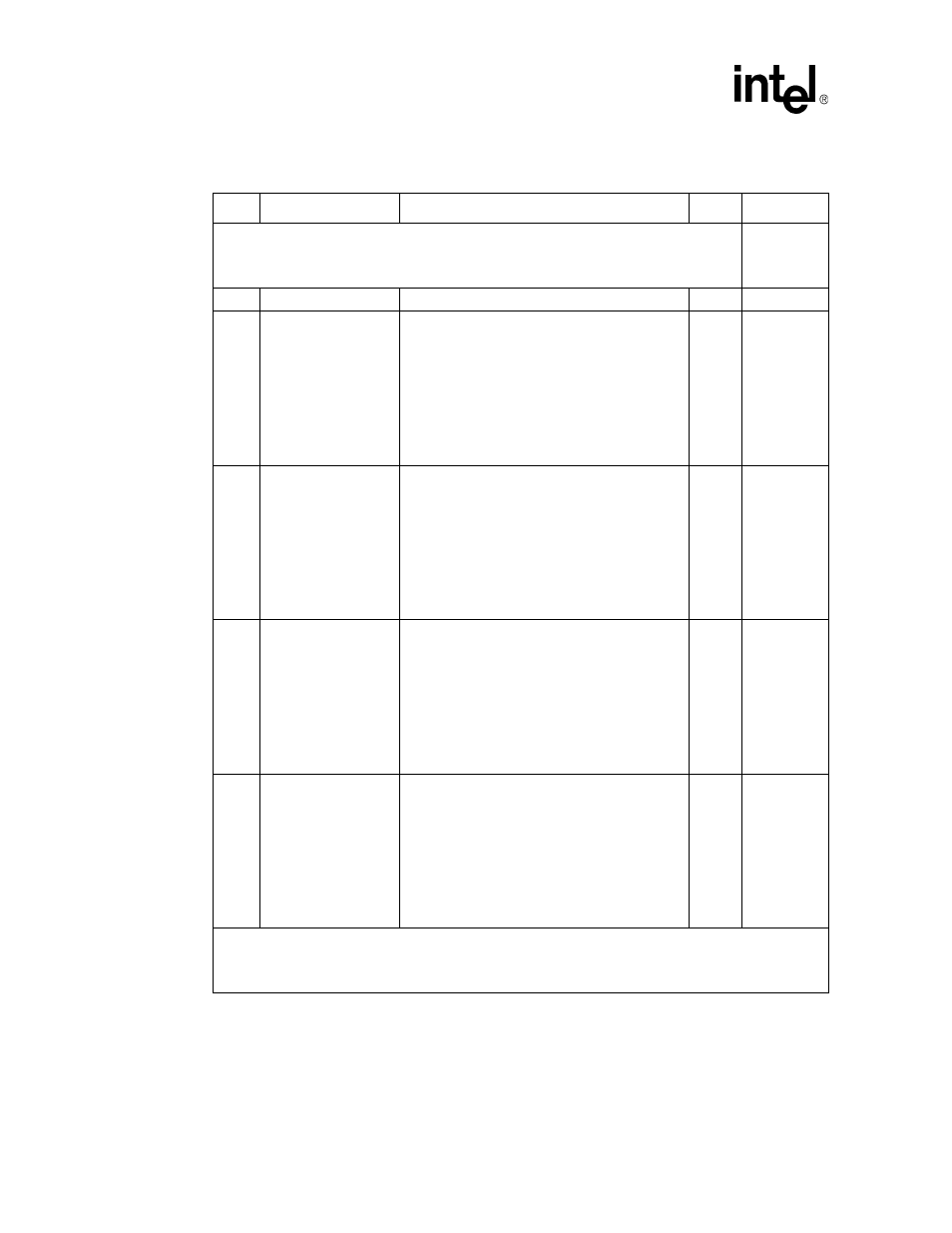

Table 152. Clock and Interface Mode Change Enable Ports 0 - 3 ($0x794)

Bit

Name

Description

Type

1

Default

Register Description: This register is used when a change to the operational mode or speed

of the IXF1104 MAC is required. This register ensures that when a change is made that the

internal clocking of the IXF1104 MAC is managed correctly and no unexpected effects of the

operational or speed change are observable on the line interfaces.

0x00000000

31:4

Reserved

Reserved

RO

0x0000000

3

Clock and Interface

Mode Change Enable

Port 3

2

Enables internal clock generator for Port 3 to

sample the

“MAC IF Mode and RGMII Speed ($

0 = Set to zero when changes are being made to

“MAC IF Mode and RGMII Speed ($

.

1 = Set to 1 for the configuration changes to take

effect.

R/W

0

2

Clock and Interface

Mode Change Enable

Port 2

2

Enables internal clock generator for Port 2 to

sample the

“MAC IF Mode and RGMII Speed ($

0 = Set to zero when changes are being made to

“MAC IF Mode and RGMII Speed ($

.

1 = Set to 1 for the configuration changes to take

effect.

R/W 0

1

Clock and Interface

Mode Change Enable

Port 1

2

Enables internal clock generator for Port 1 to

sample the

“MAC IF Mode and RGMII Speed ($

0 = Set to zero when changes are being made to

“MAC IF Mode and RGMII Speed ($

.

1 = Set to 1 for the configuration changes to take

effect.

R/W 0

0

Clock and Interface

Mode Change Enable

Port 0

2

Enables internal clock generator for Port 0 to

sample the

“MAC IF Mode and RGMII Speed ($

0 = Set to zero when changes are being made to

“MAC IF Mode and RGMII Speed ($

.

1 = Set to 1 for the configuration changes to take

effect.

R/W 0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Section 6.1, “Change Port Mode Initialization Sequence” on page 130

for the proper sequence to

change the port mode and speed in conjunction with this register.