7 tx fifo register overview, Tx fifo register overview, Tx fifo high – Intel IXF1104 User Manual

Page 203: Watermark ports 0 - 3 ($0x600 – 0x603), Table 132 “tx fifo high

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

203

Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

8.4.7

TX FIFO Register Overview

through

provide an overview of the TX FIFO registers, which include the TX

FIFO High and Low watermark.

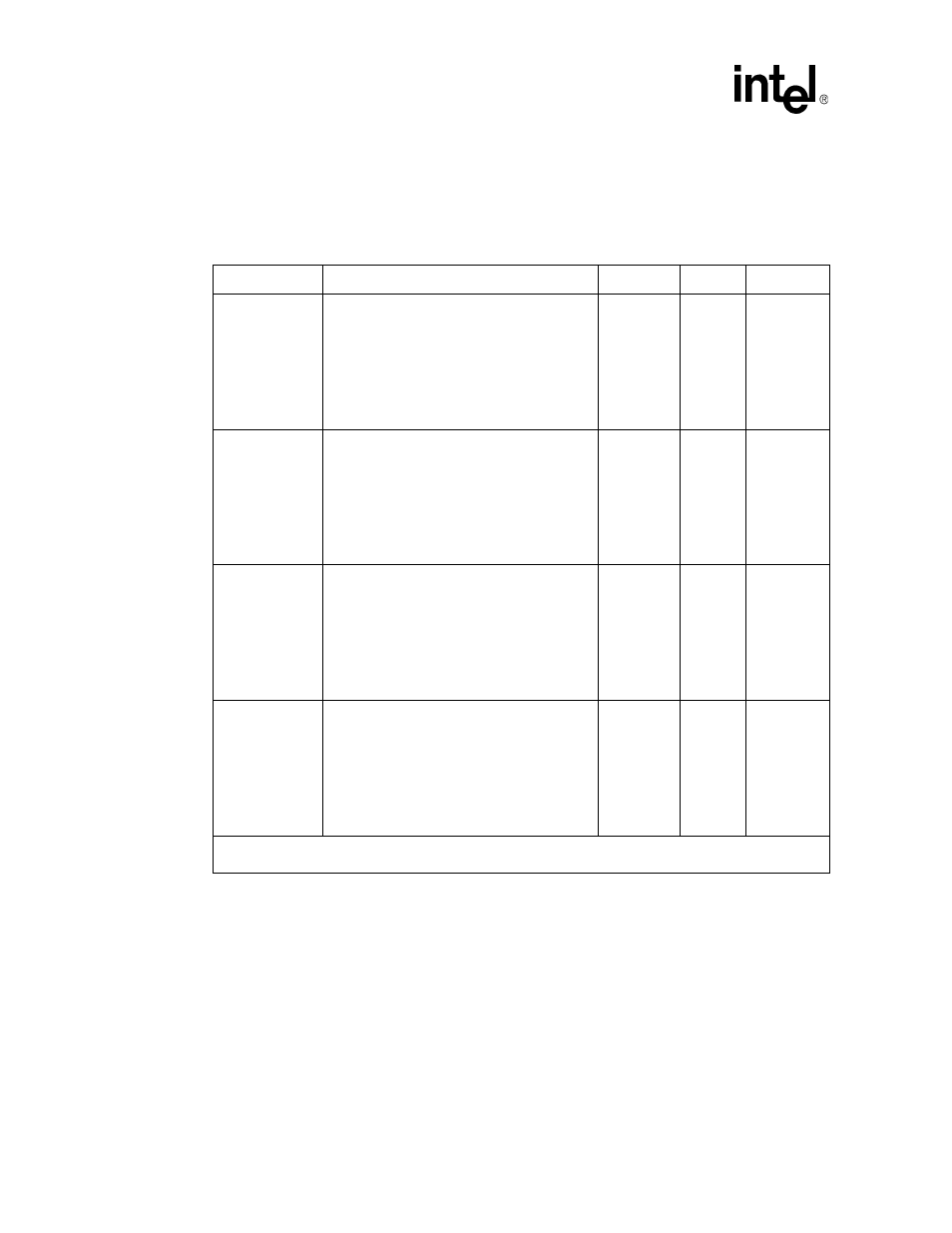

Table 132. TX FIFO High Watermark Ports 0 - 3 ($0x600 – 0x603)

Name

Description

Address

Type

1

Default

TX FIFO High

Watermark Port 0

High watermark for TX FIFO Port 0. The

default value of 0x3E0 represents 992 8-byte

locations. This equates to 7936 bytes of data. A

unit entry in this register equates to 8 bytes of

data. When the amount of data stored in the TX

FIFO exceeds the high watermark, flow control

is automatically initiated on the SPI3 interface to

request that the switch fabric stops data

transfers to avoid an overflow condition.

0x600

R/W

0x000003E0

TX FIFO High

Watermark Port 1

High watermark for TX FIFO Port 1. The

default value of 0x3E0 represents 992 8-byte

locations. This equates to 7936 bytes of data. A

unit entry in this register equates to 8 bytes of

data. When the amount of data stored in the TX

FIFO exceeds the high watermark, flow control

is automatically initiated on the SPI3 interface to

request that the switch fabric stops data

transfers to avoid an overflow condition.

0x601

R/W

0x000003E0

TX FIFO High

Watermark Port 2

High watermark for TX FIFO Port 2. The

default value of 0x3E0 represents 992 8-byte

locations. This equates to 7936 bytes of data. A

unit entry in this register equates to 8 bytes of

data. When the amount of data stored in the TX

FIFO exceeds the high watermark, flow control

is automatically initiated on the SPI3 interface to

request that the switch fabric stops data

transfers to avoid an overflow condition.

0x602

R/W

0x000003E0

TX FIFO High

Watermark Port 3

High watermark for TX FIFO Port 3. The

default value of 0x3E0 represents 992 8-byte

locations. This equates to 7936 bytes of data. A

unit entry in this register equates to 8 bytes of

data. When the amount of data stored in the TX

FIFO exceeds the high watermark, flow control

is automatically initiated on the SPI3 interface to

request that the switch fabric stops data

transfers to avoid an overflow condition.

0x603

R/W

0x000003E0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write